# Overview of 802.3bt - Power over Ethernet standard

Lennart Yseboodt, Philips Lighting David Abramson, Texas Instruments

April 2018

## IEEE 802.3bt at a glance

The new Power over Ethernet 802.3bt standard is the third revision to the widely adopted IEEE standard that specifies low voltage power transfer to networked devices. The first IEEE PoE standard, 802.3af (2003), was able to provide 13 W to devices. This was increased to 25.5 W by 802.3at (2009). With 802.3bt, the amount of power available for devices increases nearly threefold, to 71.3 W, enabling a myriad of new applications. Publication of 802.3bt is expected in the second half of 2018.

The overview below shows the power levels defined by 802.3bt and how these relate to the existing PoE standard. All PoE devices (sources or loads) are interoperable, the only limitation being that a new high power PD (Powered Device) will not get the full power from an older or lower power PSE (Power Sourcing Equipment). The different power levels are defined as 'Classes'. There are four existing Classes, providing up to 25.5 W to PDs. This is being expanded with four new Classes, taking the power level higher, up to 51 W for Type 3 PDs and up to 71.3 W for Type 4 PDs.

|         | Type 3 (802.3bt)                                                |                          |                   |                          |                        |                 | Type 4                 |                       |  |

|---------|-----------------------------------------------------------------|--------------------------|-------------------|--------------------------|------------------------|-----------------|------------------------|-----------------------|--|

|         |                                                                 | Type 1 (802.3af)         |                   | Type 2 (802.3at)         |                        |                 | (802)                  | (802.3bt)             |  |

| PSE     | Class 1<br>4 W                                                  | Class 2<br>7 W           | Class 3<br>15.4 W | Class 4<br>30 W          | Class 5<br>45 W        | Class 6<br>60 W | Class 7<br>75 W        | Class 8<br>90 W       |  |

|         | 2-pair only (Type 1 & 2)<br>2-pair or 4-pair power (Type 3 & 4) |                          |                   |                          | always 4-pair power    |                 |                        |                       |  |

| A<br>PD | Class 1<br><b>3.84 W</b>                                        | Class 2<br><b>6.49 W</b> | Class 3<br>13 W   | Class 4<br><b>25.5 W</b> | Class 5<br><b>40 W</b> | Class 6<br>51 W | Class 7<br><b>62 W</b> | Class 8 <b>71.3 W</b> |  |

This higher power level is made possible by providing current through all four twisted pairs in a network cable. The current standard (IEEE 802.3-2015/2018) only permits power transfer over two out of four pairs. For assigned Class 5 and higher, power delivery requires 4 pairs to be used. The new Type 3 / Type 4 PSEs also support existing PDs, and may also use 4 pairs to deliver power to these PDs, resulting in cable losses being halved.

In addition to more efficient power delivery and far more available power, 802.3bt has a number of new features:

**Short MPS** (Maintain Power Signature) allows PDs to achieve a much lower standby power compared to the existing standard. The minimum standby power has been reduced to  $1/10^{th}$  of what the current standard allowed (20 mW versus 200 mW). This enables IoT applications to be powered with PoE and have acceptable standby performance.

**Autoclass** is an optional classification technique that allows the PSE to account for the resistive losses in the cable and optimize the power allocation based on a reference power measurement. This allows the PSE to power more ports from a limited power supply budget.

**Power demotion** allows a PSE that cannot meet the power demand of a PD to provide it with a lower Class. The PD can then operate in a limited mode using the available power.

**Mandatory classification** is a change to the PSE rules for hardware based classification. Where Type 2 PSEs were not required to support full hardware classification, and could in stead use

LLDP (a protocol over the Ethernet data link) to provide full power to PDs, it is now mandatory for Type 3 and Type 4 PSEs to fully support hardware classification, which leads to a more robust system. LLDP is still used by PDs to fine tune their power demand.

**LLDP extensions** are a set of new fields in the LLDP protocol definition, that allow information exchange about: 4-pair capability of PDs, Autoclass, the maximum amount of power a PSE has, timed power down of a PD, measurements of voltage/current/power/energy, and the exchange of electricity price information.

#### About this document

This document provides a generic overview of how the 802.3bt IEEE Power over Ethernet standard works, with emphasis on the new elements compared to the existing standard (802.3-2015). The information herein is based on P802.3bt Draft 3.3.

While every effort is made to provide correct information, there is always the inherent risk to unintentionally deviate from what the specification actually says. This whitepaper is intended to help understand the structure and some of the more challenging parts of IEEE 802.3bt, and should not be used in lieu of the IEEE 802.3bt standard.

Each major section in the document highlights the relevant portions in the IEEE 802.3bt standard by listing these in a green box at the beginning of the section.

The focus of this white paper is to explain operation of single-signature PDs, as this is the most common PD implementation. Dual-signature operation is substantially different on most levels and will be covered in another Ethernet Alliance white paper. Unless specifically mentioned otherwise, references to "PSE" and "PD" without a specified Type, refers to Type 3 and Type 4 devices.

This document is prepared by Lennart Yseboodt (Philips Lighting, Chief Editor for IEEE P802.3bt DTE Power via MDI over 4-Pair Task Force) and David Abramson (Texas Instruments, Comment Editor for IEEE P802.3bt DTE Power via MDI over 4-Pair Task Force). The views presented in this document should be considered the personal views of the authors and not a formal position of the IEEE.

## Contents

| 1 | Intr | oduction                                     | 7  |

|---|------|----------------------------------------------|----|

| 2 | Syst | tem overview                                 | 8  |

|   | 2.1  | Power Interface                              | 10 |

|   | 2.2  | Class                                        | 10 |

|   | 2.3  | Device Types                                 | 10 |

|   | 2.4  | Cable / link section requirements            | 12 |

|   | 2.5  | 2-pair and 4-pair powering                   | 13 |

| 3 | Dete | ection                                       | 14 |

| 4 | Con  | nection check and PD signature configuration | 16 |

|   | 4.1  | Single-signature PD configuration            | 16 |

|   | 4.2  | Dual-signature PD configuration              | 18 |

|   | 4.3  | Requirements to provide 4-pair power         | 19 |

| 5 | Clas | ssification                                  | 20 |

|   | 5.1  | Classification terminology                   | 24 |

|   | 5.2  | Class probing                                | 25 |

|   | 5.3  | Mutual identification                        | 26 |

|   | 5.4  | Data Link Layer Classification               | 27 |

| 6 | Auto | oclass                                       | 28 |

|   | 6.1  | PSE Autoclass requirements                   | 30 |

|   | 6.2  | PD Autoclass requirements                    | 31 |

| 7 | Inru | ısh                                          | 31 |

|   | 7.1  | PSE inrush                                   | 32 |

|   | 7.2  | PD inrush                                    | 32 |

| 8 | Ope  | erating power                                | 34 |

|   | 8.1  | PD power limits                              | 34 |

|   | 8.2  | PSE power                                    | 36 |

|   | 8.3  | Powering configurations                      | 38 |

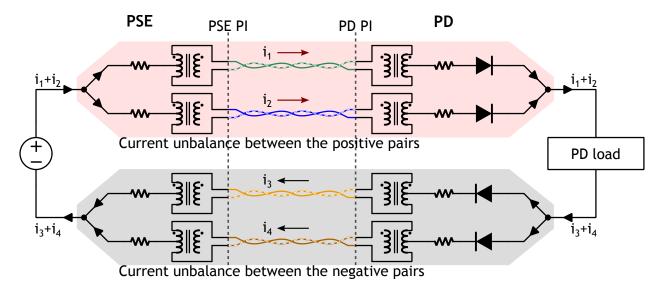

| 9  | Curr  | rent unbalance                                                                     | 41 |

|----|-------|------------------------------------------------------------------------------------|----|

|    | 9.1   | PSE current unbalance                                                              | 42 |

|    | 9.2   | PD current unbalance                                                               | 43 |

| 10 | Mair  | ntain Power Signature (MPS)                                                        | 43 |

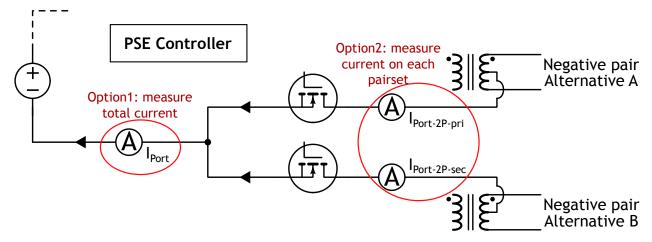

|    | 10.1  | PSE MPS measurements                                                               | 46 |

|    | 10.2  | PD MPS design consideration                                                        | 46 |

| 11 | LLDI  | P Power over Ethernet TLV                                                          | 49 |

|    | 11.1  | Power via MDI Measurements TLV                                                     | 51 |

| Ľ  | ist o | of Figures                                                                         |    |

|    | 1     | Power over Ethernet major components                                               | 8  |

|    | 2     | Power Interface (PI)                                                               | 10 |

|    | 3     | Supplying power over 2 pairs                                                       | 13 |

|    | 4     | Supplying power over 4 pairs                                                       | 13 |

|    | 5     | PSE and PD effective resistance detection parameters                               | 15 |

|    | 6     | Voltage vs current plot of a valid PD detection signature                          | 15 |

|    | 7     | Concept diagram of a single-signature PD                                           | 16 |

|    | 8     | Voltage vs current plot of a PD with 5 V applied to the other Mode                 | 17 |

|    | 9     | Voltage vs current plot of a PD with 150 $\mu A$ applied to the other Mode         | 17 |

|    | 10    | Concept diagram of a dual-signature PD                                             | 18 |

|    | 11    | Decision diagram to enable 4-pair power                                            | 19 |

|    | 12    | Type 2 Physical Layer classification timing diagram                                | 21 |

|    | 13    | Type 3 and Type 4 Physical Layer classification timing diagram                     | 21 |

|    | 14    | Autoclass Physical Layer classification timing overview                            | 29 |

|    | 15    | Autoclass PSE power measurement and PD maximum power draw timing                   | 30 |

|    | 16    | PSE total inrush current, $I_{Inrush}$                                             | 32 |

|    | 17    | PD inrush time phases                                                              | 34 |

|    | 18    | PD input average power and peak power                                              | 36 |

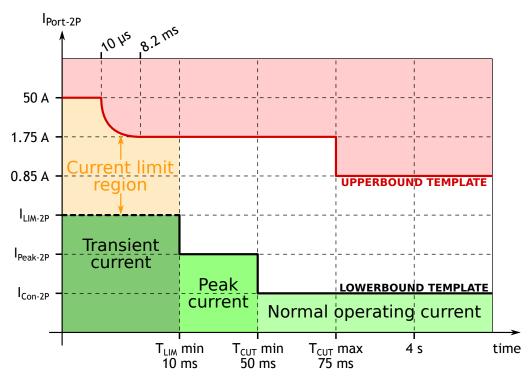

|    | 19    | Type 3 PSE operating current template                                              | 39 |

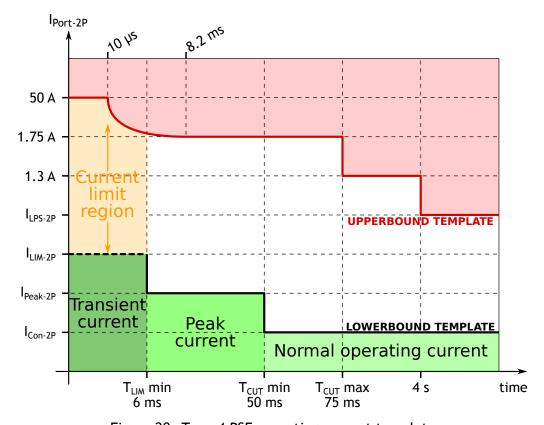

|    | 20    | Type 4 PSE operating current template                                              | 39 |

|    | 21    | PSE pinout configuration and permissible power supply polarity $\dots \dots \dots$ | 40 |

|    | 22    | Overview of pair-to-pair current unbalance in 4-pair systems                       | 42 |

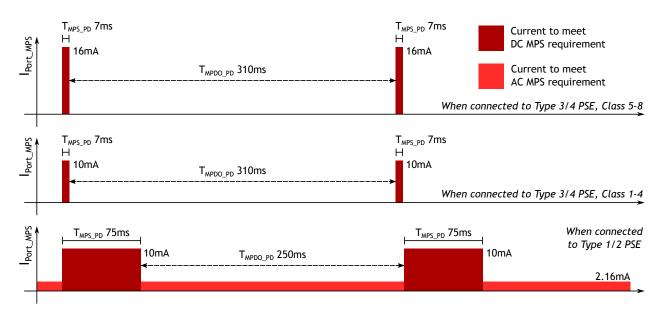

| 23 | PD MPS requirements                                                                          | 45 |

|----|----------------------------------------------------------------------------------------------|----|

| 24 | PSE MPS presence / absence determination methods                                             | 47 |

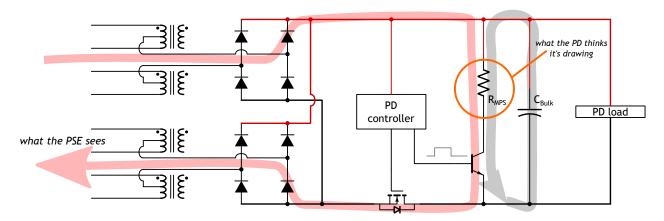

| 25 | Example PD MPS circuit that partly draws current from the bulk capacitor $\ \ldots \ \ldots$ | 48 |

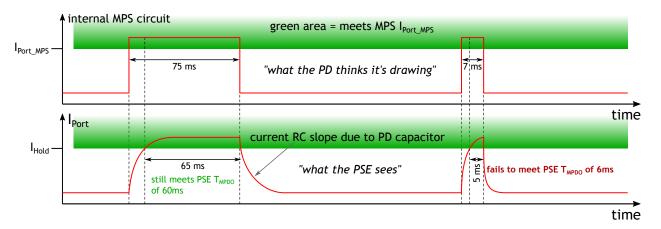

| 26 | PD capacitor causing MPS pulses to be parrower than expected due to RC effect                | 48 |

## 1. Introduction

Power over Ethernet is a technology to transfer a limited amount of low voltage DC power over a standard communication cable, concurrent with the Ethernet data flow. While a number of technologies exist that offer power transfer under the name "PoE", by far the most widely used is the IEEE 802.3 Power over Ethernet standard.

While superimposing a DC voltage on a network cable isn't hard — all it takes is a voltage source and a couple of data transformers with a center tap after all — doing so in a safe and interoperable way is not trivial. Great effort was spent to ensure that all devices compliant to the IEEE Power over Ethernet standard work with one another. The first PoE standard published in 2003 and counted 58 pages. New standards in 802.3 typically live in their own chapter, called a 'Clause' in the 802.3 document. The 802.3af amendment created Clause 33, titled "Data Terminal Equipment (DTE) Power via Media Dependent Interface (MDI)." This PoE standard supported up to 13 W for a PD, and introduced the majority of the concepts that exist in the standard today.

The need for higher power soon kicked off the successor project, 802.3at, published in 2009, counting 92 pages. The "DTE Power enhancements" Task force completely replaced Clause 33 with new text that describes both the "af" standard and the new "at" standard. This amendment (and Clause 33) were titled "Data Terminal Equipment (DTE) Power via the Media Dependent Interface (MDI) Enhancements." While consistent with the original, this title did not have a clear link to the popular term "Power over Ethernet" used in the industry. We'll come back to that later on.

802.3at introduced the concept of a device "Type". Type is a container of a number of key specifications for a given device, and is part of the device's identity. Type 1 refers to the 802.3af specification, whereas 802.3at introduced Type 2, which increased the power level to 25.5 W for the PD. Type 1 and Type 2 are fully interoperable, a Type 2 PSE will happily power a Type 1 PD, and a Type 1 PSE will power a Type 2 PD. Obviously, there is no way to get more than 13 W out of a Type 1 PSE, but the system is designed such that a Type 2 PD will recognize it is being powered by an (older) Type 1 PSE, and can only draw 13 W.

In 2013, once again fueled by a need for more power, the 802.3bt study group began the task of defining power delivery over 4 pairs. Currently at Draft 3.3 in IEEE-SA Sponsor Ballot, the standard numbers 175 pages. The additional complexity is in part caused by the need to be interoperable with the existing standard, which in itself is already an expanded version of the original. Instead of trying to describe the new Types and 4-pair power in Clause 33, we chose to create a new Clause for the new standard. The new Clause still provides full interoperability between all the device Types. The two Clauses were also given a more sensible title, Clause 33 is now titled "Power over Ethernet over 2 Pairs" and Clause 145 is titled "Power over Ethernet".

With 802.3 now claiming the term "Power over Ethernet" clearly in the title of the specifying Clause, a first step is taken to tackle the industry confusion around the term. The Ethernet Alliance has developed a certification program for PoE products based on IEEE 802.3-2015. Further information about this program may be found at <a href="https://ethernetalliance.org/poecert/">https://ethernetalliance.org/poecert/</a>. Work is currently underway to create the second generation of the certification program to address products based on the IEEE 802.3bt standard. Organizations interested in this effort should contact poecertification@ethernetalliance.org.

802.3bt introduces two new Types: Type 3, which supports up to 51 W delivered to a PD, and Type 4, which supports up to 71.3 W delivered to a PD. Consider Type 3 the replacement/upgrade of

the existing standard, while doubling the amount of power for the PD. Type 4 is the high power Type, able to provide more than 51 W to the PD. Type 4 PSEs have a higher minimum output voltage, which reduces the required current to provide these high power levels. Type 4 PSEs are also required to regulate their output power not to exceed 99.9 W for longer than 4 seconds to stay within the definition of a Limited Power Source (LPS). Type 3 PSEs may not exceed LPS power for any time duration.

The Type 3 specification's first four Classes are identical to those in Clause 33 (Type 1 and Type 2) to ensure complete interoperability between the "old" Type 1 and Type 2 devices and the "new" Type 3 and Type 4 devices. As such, 802.3bt aims to eventually obsolete the older Power over Ethernet standard in Clause 33, while retaining full backwards compatibility.

## 2. System overview

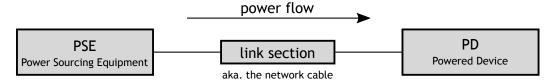

A Power over Ethernet system consists of a PSE (Power Sourcing Equipment) connected to a PD (Powered Device) through a link section. "Link section" is the 802.3 term for the cable connecting the PSE to the PD. The PSE delivers power to a PD, by applying a voltage to the network cable. The PD consumes the power sourced by the PSE.

When a PD is connected to a PSE, the general order of events is as described in Table 1. IEEE 802.3 Power over Ethernet defines mandatory checks that prevent voltage being applied unless a valid PD is connected.

Figure 1: Power over Ethernet major components

There are two kinds of PSEs. "Endpoint PSEs" are Ethernet data switches that have built in PSE functionality. A "Midspan PSE" on the other hand is inserted between a switch on one end, and to the PD on the other and injects power onto the link segment. This allows PoE to be added on any Ethernet link that does not have power by inserting a Midspan PSE in between.

Table 1: Typical startup procedure for a Power over Ethernet system

Connection between the PSE and the PD is made.

**Detection** The PSE will probe the pairset (or pairsets) for a PD. Power is ap-

plied only when a valid PD detection signature is found. PSEs that are configured to apply 4-pair power will perform detection on both

pairsets.

**Connection check** If the PSE is configured to apply 4-pair power, it will perform a con-

nection check to discover if the connected PD is a single-signature PD or a dual-signature PD. Connection check does not necessarily happen after detection, it can happen before, concurrently with, or after detection. Connection check is exclusive to Type 3 and

Type 4 PSEs that are 4-pair capable.

Classification After the PSE has performed successful detection (and connection

check if applicable) it proceeds with classification. Classification performs two functions: the PSE discovers how much power the PD

wants, and it informs the PD how much power it may draw.

**Inrush** The first phase of delivering power to the PD is called inrush. During

inrush the PSE actively limits the amount of current that flows. The purpose of this is to prevent excessive inrush current to flow when

the PD starts up.

**Powering** This is the operational phase, the PSE monitors the current/power

draw and disconnects the PD in case it exceeds a set limit. The PSE also checks if the PD becomes disconnected, in which case power

is removed from the port.

Power removal Power may be removed for a number of reasons, for example the

PD is disconnected from the PSE, the PSE no longer has power available, the PD draws excess power, or there is a short circuit in the

cable.

#### 2.1. Power Interface

An important concept in the standard is the Power Interface, or PI. The PI is the physical point where the cabling connects to the PSE or to the PD. In essence it is where the two modular connectors touch. All specifications in the standard apply at the PI, anything inside the PSE or PD is considered "implementation specific".

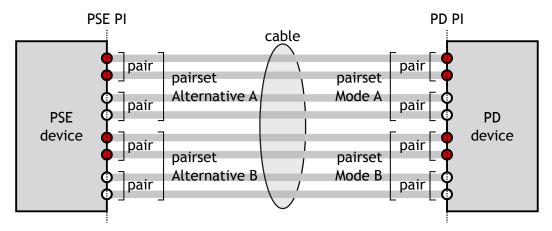

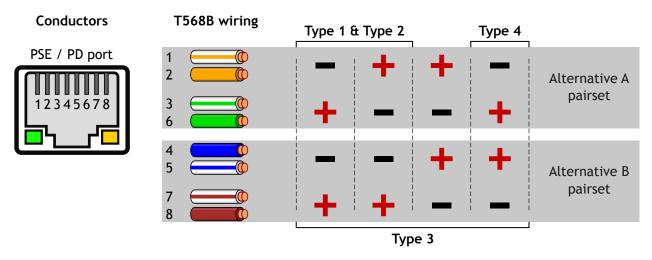

The PI consists of 8 individual contacts, that correspond to the 8 conductors in a communication cable. Two conductors form a pair (a twisted pair in the cable), both always at the same nominal voltage. There are four pairs. A pairset consists of a positive and a negative pair. There are two pairsets, which are called Alternative A and Alternative B for the PSE, and Mode A and Mode B for the PD. The relations between these concepts is shown in Figure 2.

Figure 2: Power Interface (PI)

#### **2.2.** Class

The power Class is a key concept in the Power over Ethernet standard. The Class defines the maximum power being sourced or drawn in the system. There are eight Classes, numbered 1 through 8, where 8 represents the highest power level. Class 0 (an alias for Class 3) is defined in Clause 33, but deprecated in Clause 145. Many of the device parameters and requirements depend on the (assigned) Class. For more details see Section 5.

## 2.3. Device Types

The device Type determines the major static characteristics of the PSE and the PD. An overview of the key characteristics of each Type is shown in Table 2 for PSEs and Table 3 for PDs.

Type 1 and Type 2 PSEs only provide power over 2 pairs. A Type 3 PSE can either be capable of only 2-pair power, in which case it can support up to Class 4 (25.5 W PDs), or it can be capable of supplying 4-pair power in which case it can support up to Class 6 PDs (51 W). A Type 4 PSE is always capable of 4-pair power and can support up to Class 8 PDs (71.3 W). Note that PSEs are not required to be able to support the maximum Class of the given Type, the actual rules are:

| PSE Type    | Class support requirements                                               |

|-------------|--------------------------------------------------------------------------|

| Type 1 PSEs | must be able to support at least Class 1, and may support up to Class 3. |

| Type 2 PSEs | must be able to support Class 4.                                         |

| Type 3 PSEs | must be able to support at least Class 1, and may support up to Class 6. |

| Type 4 PSEs | must be able to support at least Class 7, and may support Class 8.       |

In addition to the highest Class a PSE supports, it also supports all the lower Classes (eg. A Type 2 PSE supports Class 0, 1, 2, 3, and 4).

Unless explicitly mentioned otherwise, this document refers to Type 3 and Type 4 devices. In the standard this is similarly handled: in Clause 33, "PSEs" or "PDs" refers to Type 1 and Type 2 devices, where in Clause 145 it refers to Type 3 and Type 4 devices, unless explicitly mentioned.

Table 2: PSE Type overview

|        |                | 802.3<br>Clause | Max<br>power | Max<br>Class | Hardware classification | Autoclass | Short MPS |

|--------|----------------|-----------------|--------------|--------------|-------------------------|-----------|-----------|

| Type 1 | 2-pair only    | 33              | 15.4W        | 3            | optional                | ×         | ×         |

| Type 2 | 2-pair only    | 33              | 30 W         | 4            | optional                | ×         | ×         |

| Type 3 | 2-pair only    | 145             | 30 W         | 4            | <b>✓</b>                | optional  | <b>✓</b>  |

| Type 3 | 4-pair capable | 145             | 60 W         | 6            | <b>✓</b>                | optional  | <b>✓</b>  |

| Type 4 | 4-pair capable | 145             | 90 W         | 8            | ✓                       | optional  | <b>✓</b>  |

Table 3: PD Type overview

|        | 802.3 Clause | Max power | Classes    | Autoclass |

|--------|--------------|-----------|------------|-----------|

| Type 1 | 33           | 13 W      | 0, 1, 2, 3 | ×         |

| Type 2 | 33           | 25.5 W    | 4          | ×         |

| Type 3 | 145          | 51 W      | 1 to 6     | optional  |

| Type 4 | 145          | 71.3 W    | 7, 8       | optional  |

## 2.4. Cable / link section requirements

The Power over Ethernet standard defines several important terms related to the DC resistance of the link section. Correct operation is guaranteed for a "maximum pairset DC loop resistance" of up to  $12.5\,\Omega$ . But what does that mean? Let's explain some terms used in the standard.

**conductor** A network cable consists of 8 individual conductors, with a typical wire gauge between 26 AWG and 22 AWG.

twisted pair A twisted pair consists of two conductors twisted per a certain twist ratio. Power over Ethernet uses the common mode of these pairs to transfer DC power, without disturbing the data. The two conductors on a given pair are at the same nominal voltage and conduct current in the same direction.

pairset A pairset consists of two twisted pairs that together allow the transfer of power. One pair in the pairset is at the positive voltage, the other pair is at the negative voltage. When we say "supply power over 2-pair", this means that one pairset (thus, 2 pairs) is being used. The pairsets have specific names:

| PSE name      | PD name | cable pair colors |  |  |

|---------------|---------|-------------------|--|--|

| Alternative A | Mode A  | green and orange  |  |  |

| Alternative B | Mode B  | blue and brown    |  |  |

$R_{Ch}$  This parameter is defined as the "maximum pairset DC loop resistance" with a fixed value of 12.5  $\Omega$ . A loop resistance is the cable resistance the electrical current would encounter from the source to the load and back through a single pairset. Note that this parameter represents the worst-case value.

$R_{Chan}$  This parameter is the "actual DC resistance from the PSE PI to the PD PI and back". It represents the actual resistance in the system. In case of 2-pair powering, it is the loop resistance of the active pairset, with a maximum value of  $R_{Ch}=12.5\,\Omega$ . In case of 4-pair powering it is the loop resistance of both pairsets in parallel, with a maximum value of  $R_{Ch}/2=6.25\,\Omega$ . This parameter is mostly used for specifications dealing with single-signature PDs.

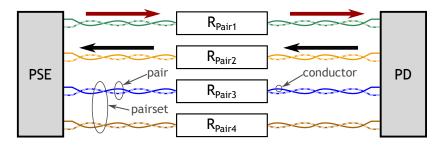

- For 2-pair mode, as shown in Figure 3,  $R_{Chan} = R_{Pair1} + R_{Pair2}$ .

- For 4-pair mode, as shown in Figure 4,  $R_{Chan} = (R_{Pair1} || R_{Pair3}) + (R_{Pair2} || R_{Pair4})$ .

$R_{Chan-2P}$  This parameter is the "actual DC pairset resistance from the PSE PI to the PD PI and back". It represents the actual resistance in the system of a particular pairset, and is mostly used for specifications dealing with dual-signature PDs.  $R_{Chan-2P}$  is thus either  $(R_{Pair1} + R_{Pair2})$  or  $(R_{Pair3} + R_{Pair4})$

Refer to Section 4 for information on single-signature PDs and dual-signature PDs.

## 2.5. 2-pair and 4-pair powering

Two powering modes exist: 2-pair mode, as depicted in Figure 3, and 4-pair mode, as depicted in Figure 4. Type 1 and Type 2 PSEs exclusively provide power in 2-pair mode. Type 3 PSEs can be constructed to be capable of 4-pair powering, or restricted to 2-pair powering. Type 4 PSEs are capable of providing 4-pair power.

The *capability* to provide power over 4-pair is distinct from what the PSE will actually do. In order to be permitted to deliver 4-pair power, a number of preconditions must be met (see Section 4.3). Furthermore, for Class 1 through Class 4 power, a PSE is permitted to either use 2-pair or 4-pair powering. It may also freely switch between 2-pair and 4-pair mode when it is providing power. A PSE that assigned Class 5 or higher power is required to provide power over 4 pairs at all times. See Section 8 and Table 14.

When power is supplied over only 2 pairs, the power can be supplied over Alternative A (pair 1 and pair 2), or over Alternative B (pair 3 and pair 4).

Figure 3: Supplying power over 2 pairs

Figure 4: Supplying power over 4 pairs

## 3. Detection

PSE: 145.2.6 PSE detection of PDs

PD: 145.3.4 PD valid and non-valid detection signatures

Detection is the most important function in a PoE system. It determines if the remote equipment connected to a PSE is capable of receiving power (in other words, it determines if it is a PD). The detection method itself has not changed from that used by Type 1 and Type 2 devices, but some of the requirements related to detection have been expanded.

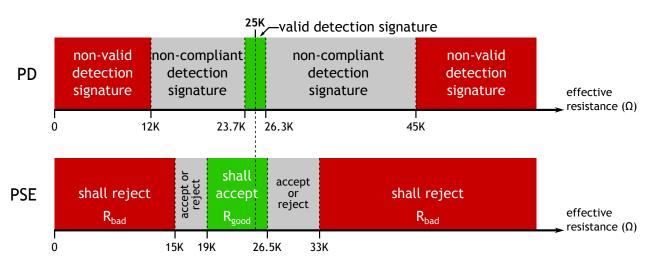

Let's start with an overview of the how detection works. During detection, the PSE measures the effective resistance of the PD using at least two voltage/current points. Note that effective resistance is not the same as taking a single (absolute) resistance measurement. By taking the difference of the two measurements the resistive slope can be determined, which is used for detection evaluation. This differential resistance measurement allows static voltage offsets in the PD to be accounted for.

$$R_{ ext{detect}} = rac{V_{ ext{detect1}} - V_{ ext{detect2}}}{I_{ ext{detect1}} - I_{ ext{detect2}}}$$

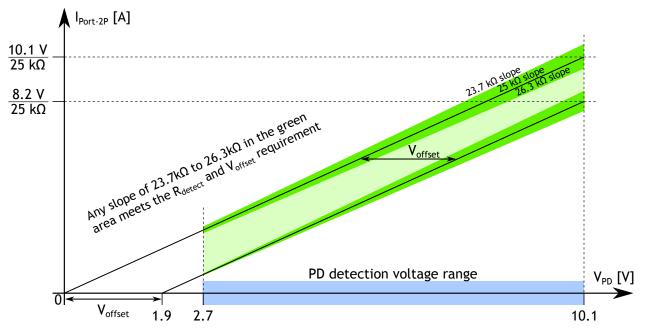

An effective resistance of  $25\,k\Omega$  signifies that the remote device is a PD and is capable of receiving power. Figure 5 shows the effective resistance requirements for the PSE and the PD.

The PSE may source a voltage and measure current, or it may source a current and measure voltage. The two measurement points must be at least 1 V apart and occur in the range of 2.8 V to 10 V at the PSE PI. As detection is used to check if the remote device is capable of accepting power, it must be done in a manner that is safe to all network equipment. Thus, the PSE cannot produce a voltage higher than 30 V and cannot source more than 5 mA of current during detection.

For Type 1 and Type 2 devices, the detection requirements are specified "at the PI" of the device, as only one pairset would ever be detected/powered at a time, since Type 1 and Type 2 PSEs provide power over 2 pairs only. For Type 3 and Type 4 devices, both pairsets can be powered and thus each pairset must be independently detected before applying power on that pairset. Under no condition can a PSE power a pairset, unless that pairset has a valid detection signature. Detection for Type 3 and Type 4 devices is specified to apply to pairsets.

In order to have a "valid detection signature" a pairset must have:

- A resistive slope between  $23.7 \, k\Omega$  and  $26.3 \, k\Omega$ , which is shown as the green triangle meets the R<sub>detect</sub> requirement, shown in Figure 6. The PD must meet this slope over the entire PD detection voltage range.

- A voltage offset (V<sub>offset</sub>) of no more than 1.9 V. Because the detection resistor (and the PD circuitry) is behind a rectifier, some voltage is lost before it reaches this resistor. For this reason, the PSE accepts the resistive slope to be shifted right by up to 2 V on the PSE side (V<sub>os</sub>).

- The PD is not allowed any current offset, however the PSE must still accept a current offset  $(I_{os})$  of up to 12  $\mu$ A. Any current offset would cause the slope line in Figure 6 to shift upward.

- An input capacitance between 50 nF and 120 nF.

- An input series inductance less than 100 µH.

The voltage offset can be calculated from the resistance measurement as follows:

$$V_{\text{offset}} = rac{V_{\text{detect2}} \cdot I_{\text{detect1}} - V_{\text{detect1}} \cdot I_{\text{detect2}}}{I_{\text{detect1}} - I_{\text{detect2}}}$$

Figure 5: PSE and PD effective resistance detection parameters

Figure 6: Voltage vs current plot of a valid PD detection signature

## 4. Connection check and PD signature configuration

PSE: 145.2.6.1 Connection check requirements

PD: 145.3.5 PD signature configurations

Two basic kinds of PDs exist: single-signature PDs and dual-signature PDs. The requirements for these two kinds of PDs are quite different, both for the PD itself, and for the PSE that is powering these devices. This document focuses on single-signature PDs and PSEs powering single-signature PDs.

Connection check is the mechanism a 4-pair capable PSE uses to probe the PD to find out if it is a single-signature configuration, a dual-signature configuration, or an invalid PD. The standard does not specify a specific method to determine the PD signature, this is considered implementation specific. An implementation can make use of the defined properties that single- and dual-signature PDs have to make its determination. These core properties are explained in Sections 4.1 and 4.2.

Detection and connection check exist for different purposes and should not be confused. Detection serves to identify an attached device as being a PD that wants to receive power. Connection check determines if the PD is single-signature or dual-signature. The result of connection check also helps to determine if a PD may be powered over 4 pairs (see Section 4.3) and how this PD will be treated by the PSE.

#### 4.1. Single-signature PD configuration

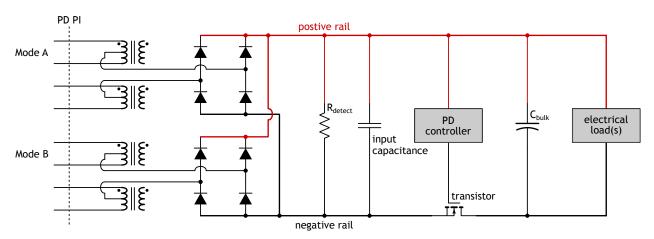

A conceptual diagram of a single-signature PD is shown in Figure 7. The essence of a single-signature PD is that both Modes are connected to the same supply rail (through the rectifiers). The detection and classification mechanism as seen through either Mode A or through Mode B is the same one. A single-signature PD has one or more electrical loads, all sharing the same supply rail.

Figure 7: Concept diagram of a single-signature PD

The requirement defining a "single-signature PD", is tricky and subtle. The standard specifies all requirements at the PI, and for this particular requirement, an indirect property had to be found that indicates both pairsets are connected together.

The requirement is twofold:

- "A single-signature PD shall present a valid detection signature on a given Mode when no voltage or current is applied to the other Mode" ...

- ... "and shall not present a valid detection signature on the given Mode when any voltage in the range of 3.7 V to 57 V is applied to the other Mode or any current greater than 124 μA is applied to the other Mode."

The first requirement is simple: have a valid detection on either pairset, when the other pairset is left alone. A valid detection signature, plotted as current versus voltage, is shown in Figure 6. A PD with a resistive slope between  $23.7\,\mathrm{k}\Omega$  and  $26.3\,\mathrm{k}\Omega$ , which is shown as the green area in Figure 5, meets the  $R_{detect}$  requirement.

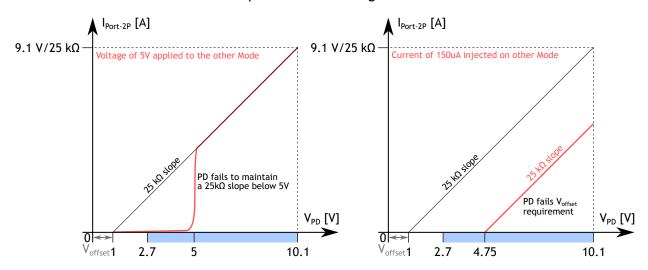

The second part of the requirement specifies what must happen to the detection signature when either a voltage is applied to the other Mode, or a current is injected. A PD that has connected both positive outputs from the rectifier into a positive rail and both negative outputs from the rectifier into a negative rail will no longer show a valid detection signature when either a voltage of at least 3.7 V to 57 V is applied, or a current of at least 124 µA is injected. The manner in which the detection signature loses validity is completely different though. This requirement is symmetric: it applies to Mode A when Mode B is manipulated with voltage or current, and applies also to Mode B when Mode A is manipulated with voltage or current.

Figure 8: Voltage vs current plot of a PD with 5 V applied to the other Mode

Figure 9: Voltage vs current plot of a PD with  $150\,\mu\text{A}$  applied to the other Mode

Take as an example a PD that has a  $V_{offset}=1\,V$  and a  $25\,k\Omega$  detection resistor. Without any influence on Mode B, the Mode A voltage/current slope would look like the black slope lines in Figure 8 and Figure 9. However when a voltage of  $5\,V$  is applied to Mode B, the resulting voltage/current plot will become similar to the red plot in Figure 8. The voltage source on Mode B prevents any current from flowing until the voltage on Mode A exceeds that of Mode B. As soon as PD PI voltage on Mode A exceeds the PD PI voltage on Mode B the current follows the expected

$25 \, k\Omega$  slope. The PD is said "not to have a valid detection signature" because it fails to maintain the correct  $R_{detect}$  slope below the voltage that is applied to Mode B.

In Figure 9 a current of  $150\,\mu\text{A}$  is injected into Mode B. The resulting voltage vs current trace is shown as the red trace, which appears as a parallel line offset below the  $25\,k\Omega$  slope. The injected current causes a voltage offset to appear over the detection resistance. Only when the voltage of Mode A exceeds that of Mode B, current can be begin to flow. In this case, while the slope is correct, the PD does not have a valid detection signature because it exceeds the  $V_{offset}$  requirement. This is an example, note that other methods can be implemented to make this determination.

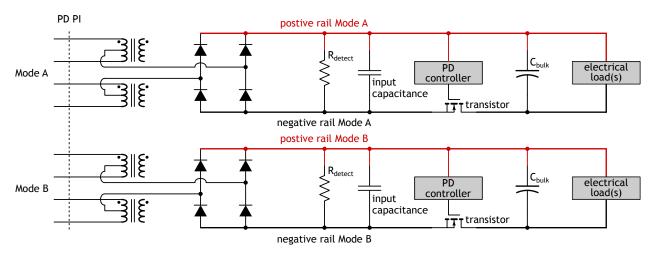

## 4.2. Dual-signature PD configuration

A conceptual diagram of a dual-signature PD is shown in Figure 10. The essence of a dual-signature PD is that both Modes connect to an individual PD controller. The detection and classification mechanism as seen through Mode A or through Mode B is a different one. This means that even if Mode A is powered, it is still possible to do detection and classification on Mode B. This would not be possible with a single-signature PD. Figure 10 shows a dual-signature PD with completely isolated loads. Other configurations are also possible, but out of scope for this overview.

The requirement that defines a "dual-signature PD" is much easier to understand: "A dual-signature PD shall present a valid detection signature on a given Mode, regardless of any voltage between 0 V to 57 V applied to the other Mode".

Figure 10: Concept diagram of a dual-signature PD

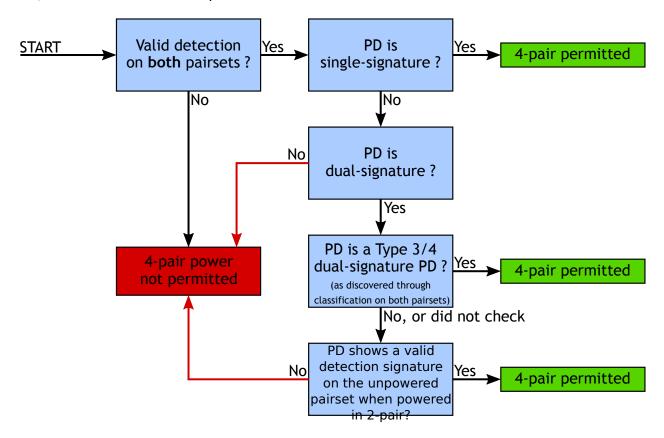

## 4.3. Requirements to provide 4-pair power

PSE: 145.2.6.7 4PID requirements

Before a PSE is allowed to provide power to both pairsets, it determines the ability of the PD to accept 4-pair power. Figure 11 shows a decision flow diagram for the PSE. Recall from the detection requirements that power can only be applied to a pairset if that pairset presents a valid detection signature (see Section 3 for detection). Thus, 4-pair power can only be applied when both pairsets present a valid detection signature. This check is the first step in the 4PID determination. All single-signature PDs may be powered over 4-pair. In case of a dual-signature PD, additional checks are required.

Indicates an abnormal issue or non-compliant PD

Figure 11: Decision diagram to enable 4-pair power

## 5. Classification

PSE: 145.2.8 PSE classification of PDs and mutual identification

PD: 145.3.6 PD classification

145.3.7 PSE Type identification

As Type 3 and Type 4 devices are introduced, one of the critical elements of interoperability is the extension of the classification mechanism. Classification is the process by which the PSE and PD negotiate the amount of power the PSE will allocate to the PD. A PD will **request** a certain amount of power, and the PSE will **assign** that power (or less, if it can't meet the demand). This process also allows PSEs and PDs to determine the Type of the device to which they are connected, referred to as mutual identification. This is done in two ways, Physical Layer classification and Data Link Layer (DLL) classification. Classification uses quite a bit of specific terminology, see Section 5.1 for an overview.

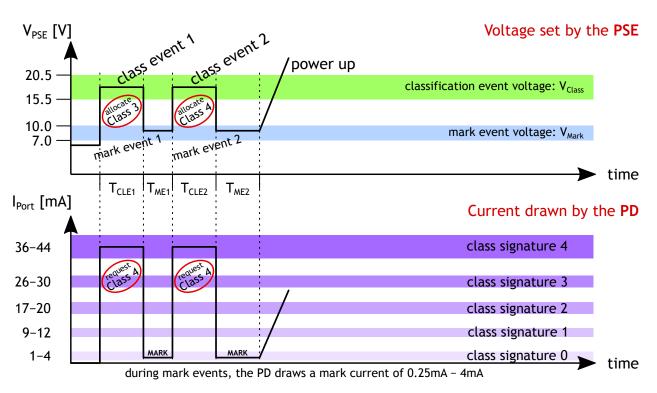

Physical Layer classification is performed after detection, but before operating voltage is applied. It consists of a series of class events during which the PSE applies a voltage level to which the PD responds with a certain predetermined current draw (the class signature). Figure 12 shows a timing diagram for a Type 2 PSE powering a Type 2 PD. In this example we see the PSE producing two class events to a Class 4 PD. The PD responds to these two class events by producing a class 4 signature for each event.

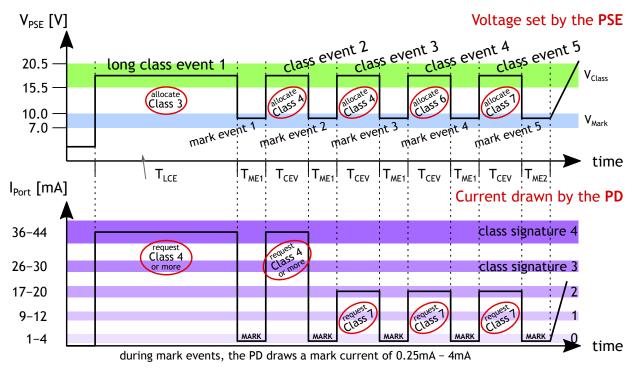

This technique has been extended for Type 3 and Type 4 and must be supported by PSEs and PDs. An example of a Type 4 PSE and a Class 7 PD is shown in Figure 13. The PSE produces 5 class events, indicating to the PD that it being assigned to Class 7.

Note that this section describes single-signature classification in detail. Dual-signature classification is substantially different, please refer to the 802.3bt standard for details.

When the PSE applies a voltage in the range of  $V_{Class}$  (15.5 V to 20.5 V) for the appropriate amount of time, this is called a class event. A class event is followed by a mark event, this is the application of voltage in the range of  $V_{Mark}$  (7 V to 10 V). A mark event allows the PD to recognize that the (previous) class event has concluded.

The relation between the PSE Type and the number of class events that can be produced is listed in Table 4.

The PD's current draw during an individual class event is named the 'class signature'. Five class signatures are defined, numbered 0 through 4, each representing a certain range of current draw

Table 4: PSE Type and corresponding maximum number of class events and assigned Class

| PSE Type | Maximum number of class events | Highest assigned Class |

|----------|--------------------------------|------------------------|

| 1        | 1                              | 3                      |

| 2        | 2                              | 4                      |

| 3        | 4                              | 6                      |

| 4        | 5                              | 8                      |

Figure 12: Type 2 Physical Layer classification timing diagram

Figure 13: Type 3 and Type 4 Physical Layer classification timing diagram

Table 5: PD requested Class and corresponding class signatures

|                 | Class signature produced by the PD |         |         |         |         |  |  |

|-----------------|------------------------------------|---------|---------|---------|---------|--|--|

| Requested Class | Event 1                            | Event 2 | Event 3 | Event 4 | Event 5 |  |  |

| Class 1         | 1                                  | 1       | 1       | /1/     | /1/     |  |  |

| Class 2         | 2                                  | 2       | 2       | /2/     | /2/     |  |  |

| Class 3         | 3                                  | 3       | 3       | /3/     | /3/     |  |  |

| Class 4         | 4                                  | 4       | 4       | /4/     | /4/     |  |  |

| Class 5         | 4                                  | 4       | 0       | 0       | /0/     |  |  |

| Class 6         | 4                                  | 4       | 1       | 1       | /1/     |  |  |

| Class 7         | 4                                  | 4       | 2       | 2       | 2       |  |  |

| Class 8         | 4                                  | 4       | 3       | 3       | 3       |  |  |

This Table shows the class signature the PD produces for each event. PDs that request Class 4 or lower always present the same class signature, regardless of how many events to which the PD is subjected. PDs that request Class 5 through 8, use a different class signature from the third event onward. A class signature denoted /between slashes/ indicates that this number of class events will not occur in a compliant system.

during a class event. The PD's requested Class is defined by the class signatures the PD presents while in the classification voltage range. See Figure 12 and 13 for a graphical representation of the current ranges that the different class signatures represent.

Table 5 shows the class signatures produced by a PD during each class event as a result of its requested Class. The PD signatures for the first two class events are the same as for Type 1 and Type 2 PDs in order to ensure backwards compatibility. During the third class event the PD can change its class signature in order to request a power level greater than Class 4. Only Type 3 and Type 4 PSEs produce more than two class events. This class signature is then repeated for any subsequent class events. The entries noted in slashes (eg. /0/) in Table 5 indicate class events that will not occur in a compliant system, but are there to define behavior for the PD if it is subjected to more class events than expected. To a Type 1 or Type 2 PSE, a Class 5 or higher PD will look like a Class 4 PD. It is only at the third class event that the PD signals that it is requesting more than Class 4 by changing the class signature.

Table 6 shows how assigned Class is determined as a result of PD's requested Class and the number of class events produced by the PSE. Simplifying even further, the assigned Class can be described as the lower of the PD's requested Class and: Class 3 if one class event is produced, Class 4 if two or three class events are produced, Class 6 if four class events are produced, or Class 8 if five class events are produced. Note that the PD class count is incremented on the class to mark transition.

While the PD is requesting power during classification, the PSE is granting or allocating power. This is done through the number of class events that the PSE produces. Table 7 shows the resulting assigned Class based on the PD's requested Class and the number of class events produced by the PSE. It also shows the extension of power demotion that is included in the Type 3 / Type 4 specification.

Table 6: Derivation of assigned Class and power levels for PSE and PD.

|                 | Number of class events |         |         |         |         |  |  |  |

|-----------------|------------------------|---------|---------|---------|---------|--|--|--|

| Requested Class | 1                      | 2       | 3       | 4       | 5       |  |  |  |

| Class 1         | Class 1                | ×       | ×       | ×       | X       |  |  |  |

| Class 2         | Class 2                | ×       | ×       | ×       | ×       |  |  |  |

| Class 3         | Class 3                | ×       | ×       | ×       | ×       |  |  |  |

| Class 4         | Class 3                | Class 4 | Class 4 | ×       | ×       |  |  |  |

| Class 5         | Class 3                | Class 4 | Class 4 | Class 5 | ×       |  |  |  |

| Class 6         | Class 3                | Class 4 | Class 4 | Class 6 | ×       |  |  |  |

| Class 7         | Class 3                | Class 4 | Class 4 | Class 6 | Class 7 |  |  |  |

| Class 8         | Class 3                | Class 4 | Class 4 | Class 6 | Class 8 |  |  |  |

This Table shows the resulting assigned Class, based on the PD's requested Class, and the number of class events that the PSE produced. A PSE may not produce more class events than what is needed to satisfy the PDs power request (eg. a PSE capable of Class 8 power is not permitted to produce five class events when the PD only requests Class 3 — the PSE may only produce one class event in this case).

A green colored cell indicates that the assigned Class is equal to the requested Class, white cells indicate that the PD has been power demoted. A cell marked with a cross indicates that the PSE is not allowed to produce the corresponding number of class events.

The term power demotion refers to a PD being assigned less power than what it asked for. In the existing standard, Type 2 PDs could be demoted to the Type 1 power level when connected to a Type 1 PSE, or power-limited Type 2 PSE, if the PSE only produced one class event. Any PD can be demoted to Class 3 power if the PSE produces only one class event, to Class 4 power if the PSE only produces two or three class events, or to Class 6 power if the PSE only produces four class events. This allows PSEs to supply power to a PD, even if the PSE does not have all of the PD's requested power available, allowing higher power PDs to operate in a reduced mode when connected to lower power PSEs.

As power demotion is critical to the understanding of Physical Layer classification, let's look at an example. Consider a system in which the PSE has 53 W available (sufficient to support Class 5, but not Class 6) and a PD is plugged in. If the PD requests Class 3 (or lower) power, the PSE will give one class event and the PD is allocated its full requested power. If the PD requests up to Class 4 power, the PSE gives either two or three class events and the PD is allocated its full requested power. If the PD requests Class 5 power, the PSE gives four class events and the PD is allocated its full requested power. However, if the PD requests greater than Class 5 power, the PSE only gives three class events and the PD is allocated Class 4 power.

There are a few other changes compared to Physical Layer classification as defined for Type 1 and Type 2 devices:

■ Type 3 and Type 4 PSEs produce a long first class event, 88 ms to 105 ms, in order to signal to the connected PD that it is connected to a Type 3 or Type 4 PSE. This allows the PD to use the short MPS timings (see Section 10). In contrast, Type 1 PSEs produce a 6 ms to 75 ms class event, and Type 2 PSEs a 6 ms to 30 ms first class event.

- The maximum length of the second through fifth class events has been reduced to 20 ms in order to reduce the thermal load on the PD controller.

- A PSE is always required to produce a mark event after the final class event prior to the application of operating voltage. This allows PDs to observe the long class event, also if it only requests Class 1 through 3, which results in a single classification event. PDs must also present a valid mark signature during this time. This is different compared to Type 1 and Type 2 classification where a mark event was not required if the PSE only produced a single class event.

- For Type 1 PDs classification is optional. A Type 1 PD that did not implement a classification circuit would present class signature 0 during a class event. A PSE treats such a Class 0 PD as if it requested Class 3. Type 3 PDs are required to support Physical Layer classification, and for this reason Class 0 does not exist for these devices. A Type 3 or Type 4 PSE connected to a Type 1, Class 0 PD, will assign the PD to Class 3, which has an identical power limit.

Table 7: Resulting assigned Class and number of class events based on available PSE power and the requested Class

|                        | Requested Class by the PD |                   |          |          |          |          |          |          |

|------------------------|---------------------------|-------------------|----------|----------|----------|----------|----------|----------|

| PSE available<br>power | Class 1                   | Class 2           | Class 3  | Class 4  | Class 5  | Class 6  | Class 7  | Class 8  |

| Class 1                | Class 1<br>(1 EV)         | no power          | no power | no power | no power | no power | no power | no power |

| Class 2                | Class 1<br>(1 EV)         | Class 2<br>(1 EV) | no power |

| Class 3                | Class 1                   | Class 2           | Class 3  |

|                        | (1 EV)                    | (1 EV)            | (1 EV)   | (1 EV)   | (1 EV)   | (1 EV)   | (1 EV)   | (1 EV)   |

| Class 4                | Class 1                   | Class 2           | Class 3  | Class 4  |

|                        | (1 EV)                    | (1 EV)            | (1 EV)   | (2/3 EV) | (2/3 EV) | (2/3 EV) | (2/3 EV) | (2/3 EV) |

| Class 5                | Class 1                   | Class 2           | Class 3  | Class 4  | Class 5  | Class 4  | Class 4  | Class 4  |

|                        | (1 EV)                    | (1 EV)            | (1 EV)   | (2/3 EV) | (4 EV)   | (2/3 EV) | (2/3 EV) | (2/3 EV) |

| Class 6                | Class 1                   | Class 2           | Class 3  | Class 4  | Class 5  | Class 6  | Class 6  | Class 6  |

|                        | (1 EV)                    | (1 EV)            | (1 EV)   | (2/3 EV) | (4 EV)   | (4 EV)   | (4 EV)   | (4 EV)   |

| Class 7                | Class 1                   | Class 2           | Class 3  | Class 4  | Class 5  | Class 6  | Class 7  | Class 6  |

|                        | (1 EV)                    | (1 EV)            | (1 EV)   | (2/3 EV) | (4 EV)   | (4 EV)   | (5 EV)   | (4 EV)   |

| Class 8                | Class 1                   | Class 2           | Class 3  | Class 4  | Class 5  | Class 6  | Class 7  | Class 8  |

|                        | (1 EV)                    | (1 EV)            | (1 EV)   | (2/3 EV) | (4 EV)   | (4 EV)   | (5 EV)   | (5 EV)   |

#### 5.1. Classification terminology

This section briefly explains the specific terminology that is key to understanding how classification works.

Class: an identifier for the maximum power consumption of a PD. Classes 1 to 8 are defined, representing an increasing maximum amount of power. For example, a Class 4 PD, is a PD that requires up to 25.5 W to operate.

**requested Class**: the Class that the PD advertises during Physical Layer classification. It represents the amount of power that the PD wants from the PSE. The requested Class is determined by the class signatures that the PD produces when exposed to class events, see Table 5.

**assigned Class**: the Class that the PSE gives (assigns) to the PD. It represents the amount of power that the PSE allocates for the PD and it also becomes the maximum power limit for the PD. A great number of PSE and PD parameters in the standard depend on the assigned Class. The assigned Class is determined based on the requested Class and the number of class events that the PSE produces, see Table 7.

**power demotion**: when a PSE assigns a lower Class than what the PD requests. This term is not used in the standard.

class event: a voltage produced by the PSE, in the range of  $V_{Class}$ , for a certain amount of time. A class event simultaneously allows the PSE to discover the requested Class of the PD (by measuring what class signature the PD produces), as well as granting a certain amount of power to the PD. Consecutive class events determine what the assigned Class is (see Table 7).

class signature: a current drawn by the PD when the PD voltage is in the range of  $V_{\text{Class\_PD}}$  (i.e. during a class event). Five class signatures are defined, numbered 0 through 4, each corresponding with a certain range of current draw. See Figures 12 and 13 to see the mapping between class current and the corresponding class signature.

class probing: a method for the PSE to determine the PD's requested Class, without the intent to allocate power or power up the PD.

classification reset: is used to reset the PD (make it forget any preceding class events) by reducing the PSE voltage below  $V_{Reset}$  for at least  $T_{Reset}$ .

mark event: a voltage produced by the PSE, in the range of  $V_{Mark}$ , which is less than  $V_{Class}$ . A mark event serves to demarcate between class events (or the last class event and power up).

mark event current: the current the PD draws during a mark event, I<sub>Mark</sub>.

**Physical Layer classification**: the entire process of a PSE producing class events, a PD exhibiting class signatures, the PSE learning about the requested Class, and finally the PSE assigning a Class to the PD. All this happens before power is applied.

**Data Link Layer classification**: the process of changing the power allocation after power is applied by negotiating a new maximum power draw using an LLDP TLV (Type/Length/Value) (see 11).

mutual identification: the process devices use to discover each other's Type.

## 5.2. Class probing

A Type 3 / Type 4 PSE is allowed to perform a 'class probe' in order to discover the requested Class of the PD. To discover this, the PSE may need as many as three class events (in case the class signature of the first class event is 4). The PSE however is not allowed to produce more than a single class event if it has a power budget limited to Class 3 or less.

To enable a PSE with a Class 3 or lower power budget to discover the requested Class, the standard allows the PSE to produce three class events, followed by a classification reset. A classification reset entails the PSE lowering the PD voltage below  $V_{Reset}$  (2.8 V) for at least  $T_{Reset}$

(15 ms). This ensures that the PD is completely reset and does not 'remember' the three probing classification events. After the probe is completed, the PSE can then issue a single class event and power up the PD.

During a class probe, the PSE is not required to produce a long first class event, it may use the the 'short' timing of 6 ms to 20 ms in order to speed up the process. The first class event that is part of normal classification is always a long first class event (88 ms to 105 ms).

#### 5.3. Mutual identification

Mutual identification allows a PSE to discover the Type of the PD to which it is connected, and a PD to learn the Type of the PSE to which it is connected. There are a few blind spots in the mechanism, as it is not always possible to determine the connected device Type. However, the specification is designed such that in case of ambiguity, the assigned Class provides all the required information to ensure interoperability.

The PSE can discover the PD's Type based on the requested Class of the PD as shown in Table 8. For PDs that request Class 4 and below it is not possible for the PSE to determine if it's a Type 3 PD, or a Type 1 / Type 2 PD.

| Table 8 | 3: Deriving | PD | Type | from | the | req | uested | Class |

|---------|-------------|----|------|------|-----|-----|--------|-------|

|         |             |    |      |      |     |     |        |       |

| Requested Class | PD Type          |  |  |

|-----------------|------------------|--|--|

| 0               | Type 1           |  |  |

| 1, 2, or 3      | Type 1 or Type 3 |  |  |

| 4               | Type 2 or Type 3 |  |  |

| 5 or 6          | Type 3           |  |  |

| 7 or 8          | Type 4           |  |  |

For the PD, Type identification of the PSE is sometimes ambiguous, but a distinction between Type 1 / Type 2 PSEs and Type 3 / Type 4 PSEs can always be made by measuring the length of the first class event. A PSE Type identification Table for the PD is provided in Table 9.

An important reason why a PD wants to know the PSE Type is to determine if it can make use of the "short MPS" feature, see Section 10 for details.

Table 9: Deriving PSE Type from the length of the first class event and assigned Class

| Duration first class event | Assigned Class | PSE Type         |

|----------------------------|----------------|------------------|

| short ( $\leq$ 75 ms)      | 1 - 3          | Type 1 or Type 2 |

|                            | 4              | Type 2           |

| long ( $\geq$ 88 ms)       | 1 - 6          | Type 3 or Type 4 |

|                            | 7 - 8          | Type 4           |

## 5.4. Data Link Layer Classification

79.3.2 Power via MDI TLV 145.5 Data Link Layer classification

Data Link Layer (DLL) classification occurs after the PD has received operating power. It operates over the Link Layer Discovery (LLDP) protocol defined in clause 79 of the IEEE 802.3 standard. All PDs, with the exception of Class 0 through Class 3 PDs, are required to support DLL classification. It is optional for PSEs to support DLL classification.

DLL classification is used for a number of reasons. Most commonly, it is used to further refine the power allocated to the PD. For example, a Class 6 PD that requests 51 W through Physical Layer classification can use DLL classification to lower its request to 43 W, allowing the PSE to recover part of the allocated power. DLL classification can also be used by PDs that did not receive their full requested power. For example a Class 8 PD that was assigned to Class 4 (power demotion) can use DLL to request Class 8 power again. If the reason the PSE assigned the PD to Class 4 was due to a lack of available power, it may later be able to reclassify the PD as Class 8 and allocate its full requested power. PDs are not allowed to use DLL to request more power than what they request through Physical Layer classification.

Two fields in the Power over Ethernet TLV (see Section 11) are used to negotiate a new power allocation between a PSE and a PD: the 'PD requested power value' field and the 'PSE allocated power value' field. These two fields are 2 bytes each, and are interpreted as an unsigned integer number.

A PD can request power by putting the amount of power it needs in the 'PD requested power value' field and sending out an updated LLDP frame. The value represents a power level in 1/10<sup>th</sup> of a Watt increments (eg. value 255 represents 25.5 W). The PSE, upon reception, will evaluate the power request, and update the allocation. It will send the new power allocation in the 'PSE allocated power value' field. Only once the PSE and PD are in sync with each other, the power allocation changes. Beware that correct implementation of DLL requires more than this short description!

A third field is noteworthy: the 'PSE maximum available power' field communicates to the PD how much power the PSE has available. It is *not* an allocation, rather it is a hint of what kind of power request the PSE would be willing to grant. To actually get the power, the PD must always use the 'PD requested power value' field and observe what happens to the 'PSE allocated power value' field.

After a DLL transaction is successfully completed, both the allocated power (PSEAllocatedPowerValue), and the PD power limit (PDMaxPowerValue) will be set to the new negotiated power level. As a result of this, it is possible that the assigned Class changes! For example, a PD that request Class 6, but gets power demoted to Class 4, will initially start with PSEAllocatedPowerValue and PDMaxPowerValue at a value of 255 (representing Class 4 power limit of 25.5 W). Later on, the PD requests what it really needs (50 W) and this is granted by the PSE, provided that it is able to allocate the requested amount of power. Now PSEAllocatedPowerValue and PDMaxPowerValue are both equal to 500. The PD has now been re-assigned to Class 6, which means that all of the class dependent requirements may have changed. A mapping between the

values of PSEAllocatedPowerValue and PDMaxPowerValue and the resulting assigned Class are listed in Table 10.

Table 10: Relation between negotiated DLL power and the assigned Class

| PSEAllocatedPowerValue (PSE) PDMaxPowerValue (PD) | Assigned Class |

|---------------------------------------------------|----------------|

| 1 - 39                                            | Class 1        |

| 40 - 65                                           | Class 2        |

| 66 - 130                                          | Class 3        |

| 131 - 255                                         | Class 4        |

| 256 - 400                                         | Class 5        |

| 401 - 510                                         | Class 6        |

| 511 - 620                                         | Class 7        |

| 621 - 999                                         | Class 8        |

## 6. Autoclass

PSE: 145.2.8 PSE classification of PDs and mutual identification

145.2.8.2 Autoclass (optional)

PD: 145.3.6.2 Autoclass (optional)

145.3.8.2 Input average power

Included in the 802.3bt standard is an optional extension of Physical Layer classification, named Autoclass. Autoclass allows the allocation of PSE power supply budget to the PD to be far better optimized than what is possible using 'normal' Physical Layer classification, or even Data Link Layer classification.

A PD can only correctly use Autoclass if it is able to put itself in a state where it consumes the maximum amount of power it needs.

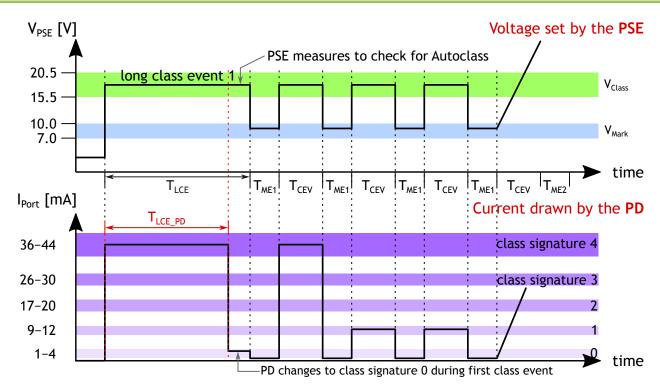

The concept of Autoclass is that a PD can request "Autoclass" during Physical Layer classification. This is done by transitioning its given (non-zero) class signature to a class signature of zero after approximately 81 ms during the first classification event. Apart from this, classification is as outlined earlier. See Figure 14 for an overview of the Autoclass Physical Layer classification specifics.

After the system has been powered, the PD will draw the maximum amount of power it needs. During this time, the PSE may measure the power consumption. That measurement of power will reveal to the PSE precisely how much power it needs to allocate for this particular PD. Because it is based on a measurement of the actual system, the resulting power budget is compensated for the actual power requirement of the PD in use, the actual cable power losses, and the power measurement uncertainty of the PSE in use.

Figure 14: Autoclass Physical Layer classification timing overview

To put this in numbers, let's say we have a Class 8 PD that requires 65 W. In our example, it is connected to the PSE by a 25 m patch cord of AWG 23. The PD is connected and gets assigned to Class 8. The PSE power supply is at 55 V. Without Autoclass, most PSEs would allocate 90 W, since that is the worst-case amount of power the PSE could be expected to source.

With Autoclass, the PD consumes 65 W (at the PD PI) after startup. The PSE power measurement will reveal that it is sourcing 66.5 W. For Class 8, a PSE is required to increase this with 1.25 W of margin, resulting in an allocation of 67.8 W. That is a difference of 22.2 W, a saving of almost 25% compared to the worst-case allocation.

Note that without Autoclass, the PSE has a number of options to improve the power allocation; using DLL classification it can learn the actual maximum power consumption of the PD, if the PSE has a better than minimum voltage power supply it can include that in it's budget calculation, and if the PSE is aware of the actual cable resistance, it can compensate its allocation for this as well. The PSE could for instance use the newly defined LLDP PoE measurements to discover the DC resistance of the cabling.

Support for Autoclass for a PSE is optional. In the case that the PSE does not implement it, but the PD does request Autoclass, the procedure outlined above still occurs for the PD, but the PSE will not make the Autoclass measurement, nor will it adjust it's power budget. The power budget will be based on the Class assigned by the PSE.

Apart from Physical Layer Autoclass, it is also possible to request an Autoclass measurement from the PSE by using the LLDP protocol. This allows a PD to use Autoclass, even if it is unable to meet the Physical Layer Autoclass timing requirement to enable the PD maximum power draw immediately after power up.

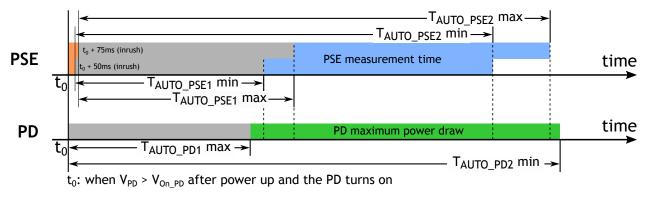

Figure 15: Autoclass PSE power measurement and PD maximum power draw timing

A common reference time  $t_0$  is used to show both the PSE and PD Autoclass timings from a common reference. The orange part of the graph is the PSEs minimum and maximum inrush time. The grey area is the wait time for the PSE before starting the Autoclass measurement. Blue is the PSE measurement time. Both minimum time periods and maximum time periods are shown, showing the extreme points of the measurements.

For the PD, grey represents the time it has to transition the load to maximum power draw. Throughout the green period, the PD is required to draw the maximum power.

## 6.1. PSE Autoclass requirements

Nearly immediately after power has been applied, the PD must consume the highest amount of power it will need for about 1.5 s and the PSE will measure the sourced power at the PSE PI to establish the power budget. A small delay is incorporated to allow the PD to conclude inrush and activate its load. The timings are shown in Figure 15 and Table 11. A PSE, after  $V_{PSE}$  exceeds 30 V, will wait for  $T_{AUTO\_PSE1}$ , and then measure power until  $T_{AUTO\_PSE2}$ . During the window between  $T_{AUTO\_PSE1}$  and  $T_{AUTO\_PSE2}$ , the PSE measures continuously and averages the power consumption with a sliding window of 150 ms to 300 ms. This results in a series of power measurements, the highest one of these determines  $P_{Autoclass}$ . The minimum power allocation for an Autoclass PSE is Class 1 power.

The PSE is required to add a small amount of margin to the power budget ( $P_{ac\_margin}$ ), with the purpose of accommodating for increased cable resistance should the cable heat up during operation. This extra margin is 0.5 W for assigned Class 1 through 4, 0.75 W for assigned Class 5 and Class 6, and 1.75 W for Class 7 and Class 8.

A potential caveat exists for PSEs that have assigned Class 1 through 4, as these are permitted to switch between 2-pair and 4-pair mode at any time. These PSEs should take into account that if they measure Autoclass in 4-pair mode, they will need to allocate additional power when the PSE switches to 2-pair mode. This extra allocation, only required while operating in 2-pair mode, is called  $P_{ac\ extra}$ , and is calculated with the highest resistance channel:

$$P_{ac\_extra} = \left(\frac{P_{Autoclass}}{V_{Port\ PSE-2P\ min}}\right)^2 \times \frac{R_{Ch}}{2}$$

Alternatively, such a PSE can choose to make the Autoclass measurement in 2-pair mode, so that

it is guaranteed to have measured the worst-case power consumption. This results in a more optimal allocation compared to making use of  $P_{ac\_extra}$ .

## 6.2. PD Autoclass requirements

After  $V_{PD}$  exceeds  $V_{On\_PD}$  (30 V to 42 V), the PD has a maximum time of  $T_{AUTO\_PD1}$  to reach a state where it is consuming it's maximum power. This is not a lot of time, nor does it allow any kind of thermal settling. Depending on the PD application it may be necessary to intentionally draw a little bit more power to accommodate thermal effects during operation. Note that Autoclass works side by side with normal classification: the PD must still meet all of the regular Physical Layer classification requirements. Autoclass can only serve to give power back to the PSE. It is also possible that an Autoclass PD gets power demoted to a lower Class, in this case the PD is still required to meet the power limitations of that lower Class.

The PSE time parameters,  $T_{AUTO\_PSE1}$  and  $T_{AUTO\_PSE2}$ , are referenced from the **end** of inrush, compared to the start of the  $T_{AUTO\_PD1}$  timer which is at the **beginning** of inrush. There is thus a 50 ms to 75 ms difference in the starting point of the PSE and PD Autoclass timing parameters. The PSE waits for  $T_{AUTO\_PSE1}$  before starting the measurement, and may measure for up to  $T_{AUTO\_PSE2}$  (referenced from the end of PSE inrush). The period during which the PSE measures the power sourced is completely within the period where the PD is required to draw maximum power, as shown in Figure 15.

Table 11: Autoclass power measurement and maximum power draw timing

| Description                      | Symbol                | min  | max  |   |

|----------------------------------|-----------------------|------|------|---|

| PD maximum power draw start time | T <sub>AUTO_PD1</sub> |      | 1.35 | S |

| PD maximum power draw end time   | T <sub>AUTO_PD2</sub> | 3.65 |      | S |

| PSE power measurement start time | $T_{AUTO\_PSE1}$      | 1.4  | 1.6  | s |

| PSE power measurement stop time  | $T_{AUTO\_PSE2}$      | 3.1  | 3.5  | S |

### 7. Inrush

PSE: 145.2.10.6 Output current during power up

PD: 145.3.8.3 Input inrush current

The inrush phase is the last phase before operating power is applied and the system begins normal operation. Inrush is the controlled application of power, to gently switch over from a non-powered state to a powered state. A large portion of interoperability problems stem from PD implementations that do not correctly implement inrush requirements. Designers are encouraged to carefully read this section, as well as the relevant sections on inrush in the 802.3bt standard.

Figure 16: PSE total inrush current, I<sub>Inrush</sub>

#### 7.1. PSE inrush

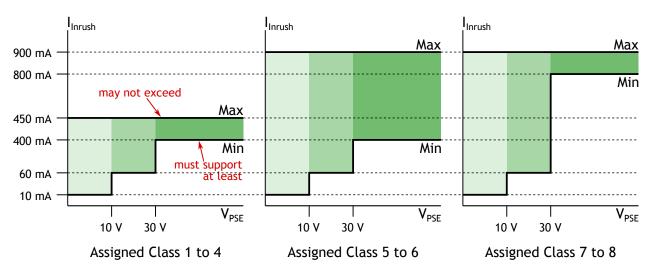

After classification, if the PSE decides to power the PD, it will first go through the inrush phase. During inrush the PSE limits the amount of current being delivered for at least  $50\,\text{ms}$  and up to  $75\,\text{ms}$ . The PSE current limit for inrush ( $I_{\text{Inrush}}$ ) depends on the assigned Class as well as the voltage at the PSE PI. This is shown in Figure 16. In order to decrease the thermal load on the PSE current limiter, the full inrush current is only required when the voltage has risen above  $30\,\text{V}$ .

In addition to the requirement on total inrush current (I<sub>Inrush</sub>), the PSE limits the current on a pairset to I<sub>Inrush-2P</sub>. For assigned Class 1 to 4, I<sub>Inrush-2P</sub> is equal to I<sub>Inrush</sub>, at 450 mA. For assigned Class 5 to 8, I<sub>Inrush-2P</sub> is 600 mA. The consequence of this is that PSEs can use 2-pair or 4-pair inrush for Class 1 to 6, but must inrush over 4-pair for Class 7 or 8 in order to meet both the pairset current limit and the total minimum inrush current.

#### 7.2. PD inrush

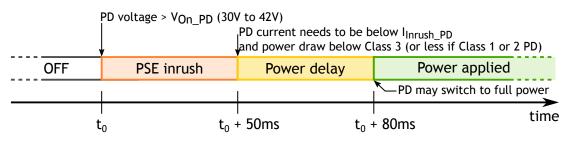

For the PD, the inrush phase begins when the PD voltage  $(V_{PD})$  exceeds the PD turn on voltage  $(V_{On\_PD})$  which is anywhere in the range of 30 V to 42 V. This moment is named  $t_0$ . The inrush phase ends 80 ms after  $t_0$ .

During the first 50 ms of the inrush phase, the PSE limits the inrush current to a total current of  $I_{lnrush}$ , and limits each pairset to a current of  $I_{lnrush-2P}$ . The values of these input currents depend on the assigned Class and on the voltage at the PSE PI (see Figure 16). During the "PSE inrush" phase there is no particular requirement on the PD.

After 50 ms the PD is in the power delay phase, which lasts for 30 ms. Somewhere in the PD power delay phase, the PSE switches from its inrush state, to its powering state. During this time, the PD needs to meet the following requirements:

- 1. Have a total input current less than I<sub>Inrush\_PD</sub> (parameter depends on the assigned Class) and have a pairset current less than I<sub>Inrush\_2P</sub> on each pairset.

- 2. Have an input **power** less than Class 3 (13 W) or the PD's requested Class, whichever is lower.

The reason for item 2 above is that the PSE can switch out of inrush at any time between 50 ms to 75 ms and immediately enforce the assigned Class.

To meet these requirements, it is highly recommended to keep the PD electrical load disabled until the PD is solidly into the 'power applied' state, as shown in Figure 17. If the load is turned on prematurely, part (or all) of the current the PSE provides is taken by that load, and prevents the bulk capacitor from charging.

There are several methods employed by PDs to complete inrush. Ultimately, only one of these can guarantee the PD to successfully complete inrush and achieve interoperability with all PSEs.

- 1. The PD does not perform any form of inrush control. Once the PSE turns on and the PD voltage has risen above V<sub>On\_PD</sub>, the PDs power switch turns on and stays on. This has the effect that the voltage at the PD PI (and PSE PI) collapses to near zero. As can be seen in Figure 16, PSEs are allowed to deliver small currents at this voltage. Unless the PSE provides significantly more inrush current that the minimum required by the standard, inrush will fail because the bulk capacitor of the PD will not be charged when the PSE transitions from inrush to power on. Such a PD fails to comply with the V<sub>Off\_PD</sub> requirement, which states that below 30 V a PD must be "turned off".

- 2. The PD does not perform inrush current limitation, but adheres to the V<sub>On\_PD</sub> / V<sub>Off\_PD</sub> requirement. Whenever the PD turns on, it will transfer the charge in its small input capacitor (maximum 120 nF) through the power switch to its larger bulk capacitor. Once the voltage is reduced to V<sub>Off\_PD</sub>, the power switch turns off. This will cause the power switch to rapidly turn on and off, essentially acting as a switched-capacitor current regulator. Besides being inefficient, such a PD violates the requirement that a PD may not oscillate during turn on.

- 3. The PD limits the inrush current below I<sub>Inrush\_PD</sub>. Once the PD turns on, it limits the inrush current to a value below I<sub>Inrush\_PD</sub> (400 mA or 800 mA). The voltage at the PD and PSE PI does not collapse back down, but quickly rises to the nominal operating voltage. Because the PD controls the inrush current, it's power switch carries the thermal load of inrush, rather than the PSE. This is in the only compliant and interoperable way a PD can charge its bulk capacitance.

Note that at  $t_0$  + 50 ms the PD, in addition to drawing less than  $I_{Inrush\_PD}$ , must conform to the power limits of the "Power delay" state. This power limit is 13 W if the PD requested Class 3 or higher, or 3.84 W or 6.49 W if the PD requested Class 1 or Class 2 respectively. The corresponding input current limits are significantly below the  $I_{Inrush\_PD}$  value.

After the power delay state, the PD has reached the nominal operating phase and can draw power up to the assigned Class. Refer to Section 8 for more information.

Figure 17: PD inrush time phases

## Operating power

PSE: 145.2.8 PSE classification of PDs and mutual identification

145.2.10 Power supply output 145.2.11 Power supply allocation

PD: 145.3.6 PD classification

145.3.8 PD power

145.3.8.2 Input average power

Following successful detection and classification a system usually spends most of its time in the nominal powering state. During this time the PSE checks for abnormal conditions, like overloads or short-circuits, as well as checking that the PD remains connected. As a result of classification, the PD will either have been assigned to the Class it requested, or may have been assigned to a lower Class (referred to as power demotion). In either case, both the PSE and the PD are required to conform to the requirements of the assigned Class. The assigned Class can also change after the system is powered on, as a result of Data Link Layer classification (see 5.4).

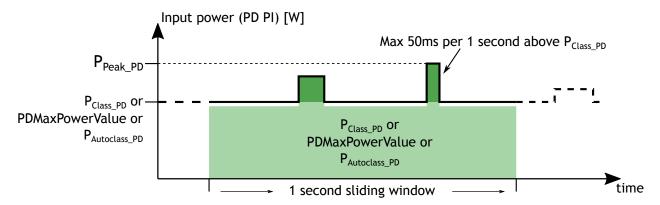

## 8.1. PD power limits