Interoperability Makes the Ethernet World Go ‘Round

By Ethernet Alliance Member, Vijay Srinivasan of Intel

Ethernet Alliance is pleased to share this perspective piece from Principal member, Intel Corporation.

Intel, a Principal Ethernet Alliance member, has created a report describing an interoperability concern arising from a gap in specifications between a 100 Gigabit (100G) PSM4 vs. 25GBASE-LR optical module. In a recent technical paper, Optical Transceiver Interoperability Concern On 25 GbE Links Utilizing 25GAUI C2M ⟷ PSM4/Lane SMF Interface, Technical Leader, Intel EPG Link Applications Engineering, Vijay Srinivasan, offers analysis and recommendations for operators and end users like telecoms and communications service providers, as well as Ethernet PHY and optical module vendors.

Interoperability Concern

During a pre-deployment build for a large scale Server-to-Switch installation of 25Gb Ethernet, an Intel TelCo customer discovered an issue surrounding the 25GAUI C2M links which materialized when pairing 25GBASE-LR transceivers with individual lanes of a 100G PSM4 transceiver in breakout configuration. A deep-dive into link failures led to the observation that stable optical domain clock recovery in a PSM4 lane receiver may not be guaranteed, even with compliance to IEEE Std. 802.3-2022™ and 100G PSM4 Ver. 2.0 2014 specifications being true for constituent link segments.

A critical factor is the non-overlapping Stressed Receiver Sensitivity (SRS) Sinusoidal Jitter Tolerance (SJTOL) specifications for 25GBASE-LR and 100G PSM4 optics. Therefore, it’s prudent to be aware that PSM4 is compatible with but not compliant to 25GBASE-LR requirements, potentially leading to link quality degradation in select circumstances.

Focus Area for Interoperability Concern

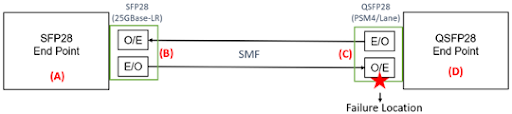

This interoperability concern manifests as PSM4 lane O/E CDR Loss of Lock (LOL) as shown in Figure 1. A likely cause for PSM4 O/E CDR LOL is a subtle impact on CDR recovered clock jitter when two or more SJ components within 10MHz bandwidth exist simultaneously at SFP28 TX (TP1a). It brings the following into focus:

- Non-overlapping SJTOL specifications applicable to 25GBASE-LR and PSM4 modules

- Impact of PSM4 lane-lane crosstalk on O/E CDR SJTOL

- Ambiguity in SJTOL compliance test related to covering pairs of SJ frequencies

- Differences between E/O and O/E signal conditioning and its impact on respective CDR JTOL function

Figure 1. 25GBASE-LR PSM4/Lane Interface point of failure

Intel’s testing, based on FEC corrected codeword count remaining at zero monitored over a seven-day period, indicates that when a module option is available, disabling PSM4/Lane O/E CDR restores the link with no link quality penalty. This option, while viable, is subject to sufficient validation and is recommended with Clause 108 RS FEC stipulated in IEEE Std. 802.3-2022 Clause 114 for interfacing with 25GBASE-LR PMD.

Industry Impact

End users with a need to deploy 25G optical links using 100G PSM4 module lanes in a breakout configuration connected to 25GBASE-LR modules must exercise caution and ensure the PSM4 module selected meets 25GBASE-LR SJTOL specification to guarantee link robustness. Additionally, the selected optical modules should meet all necessary and relevant specifications for their interconnect applications.

To learn more about further characterization tests for industry consideration in future Ethernet specifications, download “Optical Transceiver Interoperability Concern On 25 GbE Links Utilizing 25GAUI C2M ⟷ PSM4/Lane SMF Interface” now at.