Next Generation Electrical Interfaces Beyond 100G: TEF21 Panel Q&A – Part 1

Next Generation Electrical Interfaces Beyond 100G: TEF21 Panel Q&A – Part 1

Chris Lyon, Ethernet Alliance President and Amphenol

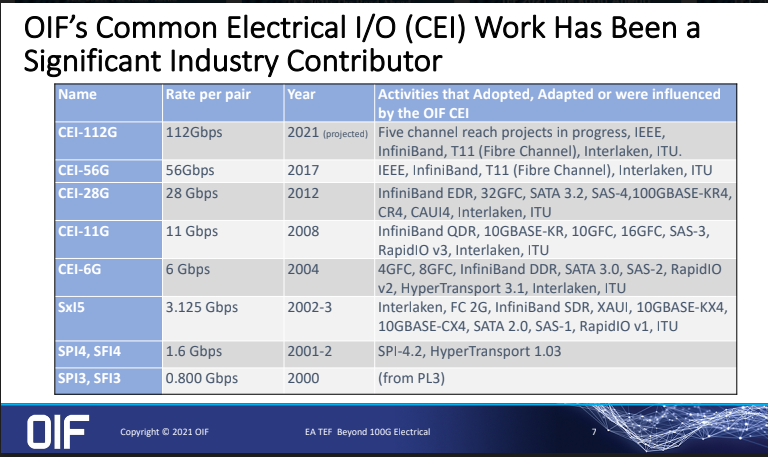

Dave Stauffer, OIF

Nathan Tracy, Ethernet Alliance Board Member and TE Connectivity

Cathy Liu, Broadcom

Ramin Farjadrad, Marvell

Key Considerations Driving Electrical Interfaces

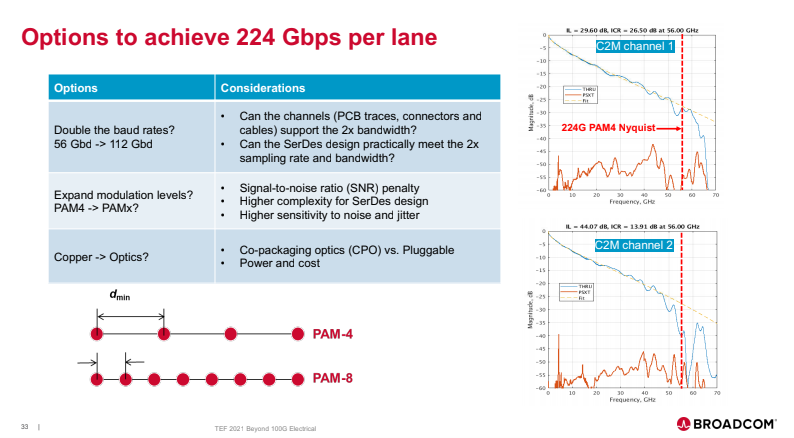

On day three of the Ethernet Alliance’s TEF21: The Road Ahead, panelists discussed the future of electrical interfaces. With faster speeds and next generation applications driving increased electrical data rates, the Next Generation Electrical Interfaces Beyond 100G moderator Chris Lyon, Ethernet Alliance Board President, along with panelists Dave Stauffer, OIF & Kandu Bus (OIF Common Electrical I/O 224G Project Overview); Nathan Tracy, Ethernet Alliance BoD and TE Connectivity (Electrical Future Work); Cathy Liu, Broadcom (Electrical Interfaces beyond 100G); and Ramin Farjadrad, Marvell (224G Dual Duplex Signaling over Single Lane Copper Links), addressed key issues and considerations surrounding the next industry rate and the interfaces needed to deliver it. Questions such as what reaches will be required, and which signaling modulation schemes will be necessary were discussed.

At the presentation’s conclusion, the audience engaged panelists with numerous questions about the technology developments needed to address escalating speed and bandwidth requirements’ impact on electrical interfaces. Their insightful responses are captured below in part one of a three-part series.

New Thinking in Electrical Interface Progression

New Thinking in Electrical Interface Progression

Chris Lyon: Should the electrical and optical 224 gig links be jointly optimized, for example, what if PAM5 is best for electrical, while PAM6 is best for optical? Wouldn’t matching FECs be ideal for example?

David Stauffer: It depends on what the application is. Not all of the applications ever go to an optical segment. In high-performance computing (HPC) for instance, there are many electrical interfaces, chip interfaces are often just electrical. You would need to optimize it for the SerDes (Serializer/Deserializer) to hit the widest possible application space. When you have applications that marry together optics and electrical, then they use that as a starting point, and they may make other considerations potentially relevant.

Chris Lyon: Is the active copper cable assumed to be continuous-time-linear-equalizer (CTLE) with re-timer as an analog or digital? Also, could you define what an active cable is?

Nathan Tracy: Sure, an active cable is one where the electronics have been embedded into both ends of the cable. Or it could even be effective if we retimed the signal only on one end. But in this case [slide 26], this is an initial cursory analysis, and so what we were simply doing is originating a signal here and sending it through the cable and terminating the cable pairs on the other end. It’s very straightforward. It didn’t go into the level of complexity of whether or not it would be fully retimed, although, you know, at this data rate, that could be a likely situation. But it would be premature to jump to that conclusion. This is simply an analysis to understand the channel. What does the channel look like? What’s the quality or the level of impairment in the channel? And so, I think as the industry moves on with this 200 gig conversation, then we’ll get into the specific channels and chip architectures that can be used. So we don’t want to put too much into it. We’re simply trying to quantify the channel, and how feasible the channel is. It’s a fairly straightforward transition from a chip fan out to a soldered termination through a cable, another solder termination, and then fan in into the received package. So, just quantifying that channel itself more so than the chip architecture that will be used.

Chris Lyon: How will these work for backward compatibility since connectors, ecosystem, etcetera will be totally different? Today all connect in data path are unidirectional.

Ramin Farjadrad: Well, no, electrical wires don’t have any direction. You can transmit or receive in either direction. The signal travels in both directions. So, it’s not like the diode that signals only travel in one direction. So, pretty much there doesn’t need to be any change in the cables, or special cables or connectors for that purpose.

Chris Lyon: Can you please comment on why Chord signaling is not considered?

David Stauffer: We have looked at Chord signaling in some applications. The fat pipe CNRZ5, is applicable to fat pipe applications on an MCM, and the 112-gig solution for MCM is based on CNRZ5. ENRZ also has a place, however the industry’s general direction has been around PAM4 application, or PAM4 modulation at 56-gig and 112-gig.

Ramin Farjadrad: One thing I can add is that Chord signaling requires running multiple lanes at the same time for its efficiency. Let’s say you need six wires to  run five different channels. So, in scenarios that you only need two channels, that will not necessarily be the optimum. For larger bandwidths or multi-lane channels, Chord signaling can be an option to consider.

run five different channels. So, in scenarios that you only need two channels, that will not necessarily be the optimum. For larger bandwidths or multi-lane channels, Chord signaling can be an option to consider.

Nathan Tracy: We’re interested in finding solutions for the industry’s challenge. From my standpoint, there is no bias against chord signaling, but we would want to see the industry momentum in that direction; so we’d be happy to bring channel analysis forward to investigate Chord, if the industry showsinterest in that direction, that would be interesting.

Cathy Liu: If the industry is showing interest in Chord signaling, then we can investigate, just like before we do the MCM as well as the Dual Duplex, right? Those things are great ideas and can really help us to solve those limitations for next generation speed node. We may need out-of-the-box ideas. Right now, from our analysis at least for XSR, VSR and even some good MR chip channels, we have a potential solution even with the traditional, the PAM4 or being a little bit higher like PAM6 modulations, we can achieve the 224 gig per second doable. However, if we really want to expand the application space to even longer or higher performance, we may need some out-of-the-box ideas.

To access TEF21: Next Generation Electrical Interfaces on demand, and all of the TEF21 on-demand content, visit the Ethernet Alliance website.