Next Generation Electrical Interfaces Beyond 100G: TEF21 Panel Q&A – Part 3

Next Generation Electrical Interfaces Beyond 100G: TEF21 Panel Q&A – Part 3

Chris Lyon, Ethernet Alliance President and Amphenol

Dave Stauffer, OIF

Nathan Tracy, Ethernet Alliance Board Member and TE Connectivity

Cathy Liu, Broadcom

Ramin Farjadrad, Marvell

Key Considerations Driving Electrical Interfaces

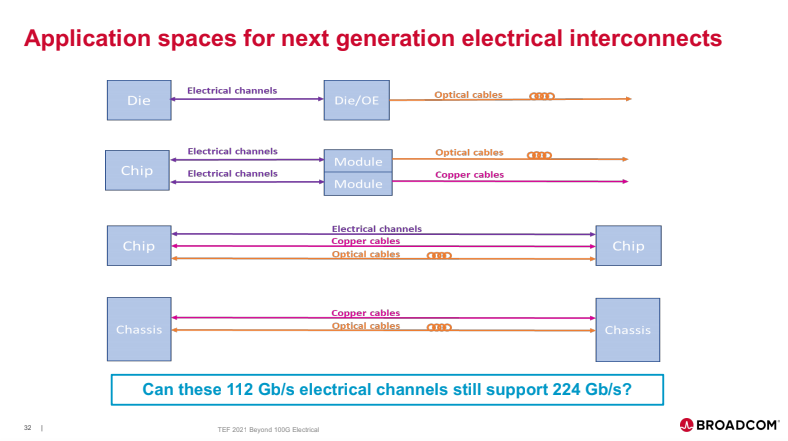

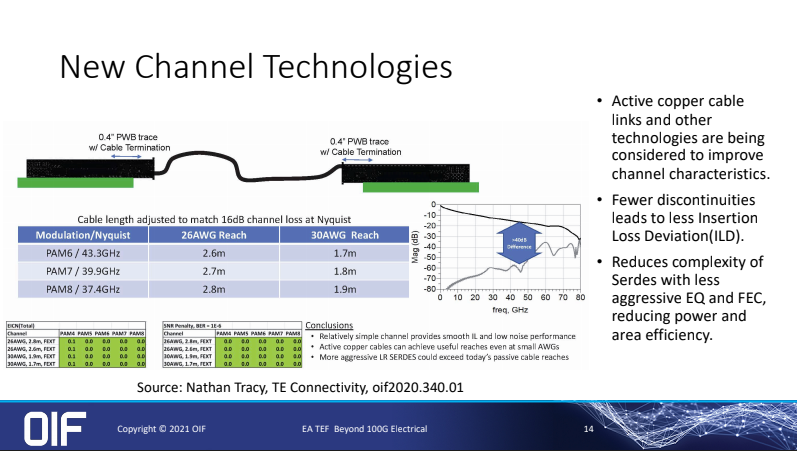

On day three of the Ethernet Alliance’s TEF21: The Road Ahead, panelists discussed the future of electrical interfaces. With faster speeds and next generation applications driving increased electrical data rates, the Next Generation Electrical Interfaces Beyond 100G moderator Chris Lyon, Ethernet Alliance Board President, along with panelists Dave Stauffer, OIF & Kandu Bus (OIF Common Electrical I/O 224G Project Overview); Nathan Tracy, Ethernet Alliance BoD and TE Connectivity (Electrical Future Work); Cathy Liu, Broadcom (Electrical Interfaces beyond 100G); and Ramin Farjadrad, Marvell (224G Dual Duplex Signaling over Single Lane Copper Links), addressed key issues and considerations surrounding the next industry rate and the interfaces needed to deliver it. Questions such as what reaches will be required, and which signaling modulation schemes will be necessary were discussed.

At the presentation’s conclusion, the audience engaged panelists with numerous questions about the technology developments needed to address escalating speed and bandwidth requirements impact on electrical interfaces. Their insightful responses are captured below in part one of a three-part series.

Channel Factors & Electrical Interfaces

Channel Factors & Electrical Interfaces

Chris Lyon: Does the SNR penalty account for only signal reduction, like eye-height reduction, or does it also account for noise reduction in the integrating over a lower noise bandwidth since Nyquist is reduced to the same data rate as the higher order modulation?

Cathy Liu: Yes, both are included. The SNR penalty we list in the table or discussed in the presentation is the SNR requirement, at the slicer of the receiver for the SerDes (Serializer/Deserializer), right? All those, you know, equalized signal versus the noise and jitter come into the slicers were added in as the entire SNR that is required for different modulation levels in order to achieve a certain BER or DER target 1e-4, 1e-5, or 1e-6, and that is the requirement for the SNR. And then I would say the answer would be include both, all the considerations, because the SNR here is a slicer SNR requirement.

Chris Lyon: Having echo cancellation in DSP will result in non-linear AFE and result in reduction in allowable signal range than ADC. Could you please comment on why echo cancellation cannot be done in analog?

Ramin Farjadrad: It can be done in analog. I mean it’s nice for short channels, we do it in analog. So, but the reason you– in some of the examples I discussed, especially the last one for two meter that’s done in digital is because when you go over a long challenge, you put in an ADC to use long (32-tap) FFEs for better signal processing and equalization, in that case you’re already in digital domain. So you can also implement echo cancellation in digital domain as well. But in previous examples like VSR, XSR, that’s something we can do in analog.

Chris Lyon: Any closing thoughts?

Cathy Liu: A lot of people asked me one question, what do you think of the next generation SerDes? Between the higher bandwidth and higher modulation levels, which one we prefer to go with? And which one is more challenging? It’s really depends on the interface we’re talking about, electrical interface or the optical interface, or have to do the joint consideration between those two altogether. In general, we know the optical interface, like fiber optics, is harder to solve the linearity issues and especially for the higher-level modulation. And they would like to take the challenge of the higher bandwidth. But for the copper, or electrical interface, we may hit the limitations on the bandwidth earlier than optical interface. So, then we may have to look at the different modulation levels or with the channel improvement, not only on the channel insertion loss, but also the return loss or crosstalk. So channel factors are tangled now. But we have the confidence and belief that down the road, maybe within the next few quarters, in the standard bodies like IEEE and OIF CEI-224G, the participants work together and do the analysis and contributions, will find a clearer path to the next generation system solution.

Ramin Farjadrad: I also agree with Cathy that we need to treat each channel and each environment separately. Given that we are approaching the signaling limits that are extremely challenging, both from silicon design development part of it, and also the channel part of it, I think we need to try to solve each channel, this problem for each channel and each environment separately to find the optimum solution for each one. And try to solve the optical solutions. Try to see what’s the best modulation, the best scheme, best FEC for that channel, and also for electrical separate from optical. I encourage the industry to explore all the options possible. For example, if we can build electrical channels that provide high enough BWs for signaling at PAM2/PAM4, we don’t have to go through echo cancelled solutions, but if we start hitting real channel limitations, we have to put all options on the table and decide what is our best bet to achieve what the industry is looking for.

To access TEF21: Next Generation Electrical Interfaces on demand, and all of the TEF21 on-demand content, visit the Ethernet Alliance website.