Improving 400/800GE optics: Is your Layer 1 FEC compliance testing enough?

Today, data center optics are rapidly transitioning to 200GE/400GE rates. In fact, the adoption of 400GE pluggable optics in the data center is in full swing, with deployments anticipated to spark in 2022. To get to this point, new silicon and circuits were required, such as linear broadband amplifiers and drivers, and adaptive digital equalizers to handle the PAM4-based 400G interfaces. As with any new optics technology, standards were developed and ratified and new test solutions were developed to validate the new standards.

With 400GE optics mass deployment around the corner, the data center interconnect (DCI) ecosystem now has its eye on 800GE rates, as bandwidth and performance demands on the network continue to accelerate.

In this blog, we will look at current testing for 400GE optics and test considerations for the next-generation 800GE rates.

Key tests for 400GE optics

Optics vendors exert great effort to differentiate their products by minimizing/optimizing power budgets, reducing noise, and operating within IEEE specs. Even with that careful tuning, 400G links can have substantial bit error rates (BER), so forward error correction (FEC) is now a requirement for 400G rates. Additionally, because there can be component and system design tradeoffs while FEC is “turned on”, predicting the FEC margin under real conditions (i.e., stress on the link) is critically important.

To fully test the system, you will want to perform BER test (BERT), FEC error density, and FEC margin tests of the optical transceiver module itself and the associated host application-specific integrated circuit (ASIC).

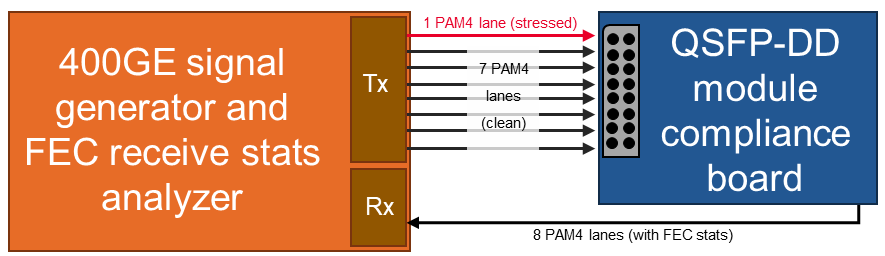

To avoid validation pitfalls, 400GE and 800GE FEC-aware receiver testing should include frame loss ratio (FLR) testing in 400/800GE links with one lane of stressed FEC-encoded test pattern (using a BERT) while the other lanes are supplied with non-stressed data that is aligned and properly encoded with the FEC test pattern.

Very soon, we will see more advanced testing techniques emerge that bridge the physical world (i.e., line-side optics) with the electrical domain (client-side optics). High bandwidth transmissions at 800G rates will need more sophisticated analysis techniques to troubleshoot and correct link performance. For example, burst packets in the network are commonplace, and can greatly affect network performance by causing packet drops in routers. Correlating FEC error density, on a per electrical lane basis, while viewing the physical behavior of the link, allows engineers to quickly find problem areas and make design and validation corrections.

Figure 1: To measure FLR under stress conditions, use a testbed with one lane of stressed FEC-encoded test pattern while the other seven lanes contain properly-aligned striped FEC traffic

This testbed enables other critical validation results such as:

- Per-lane Raw BER (unstressed)

- Pre-FEC BER

- Error distribution across FEC codeword

- Error density across all lanes

- Common Management Interface Specification (QSFP-DD MSA) – viewing register information of the optical transceiver, such as power dissipation

Conclusion

Test solutions should provide fast, accurate, and repeatable optical and electrical stress signal calibration to validate interoperability and design margin requirements. New 400G and now 800G optical transceiver modules may benefit by validation that considers BERT and FEC testing, and addresses testing of 400GE-class optical transceiver modules and associated host ASIC.