Next Generation Electrical Interfaces Beyond 100G: TEF21 Panel Q&A – Part 2

Next Generation Electrical Interfaces Beyond 100G: TEF21 Panel Q&A – Part 2

Chris Lyon, Ethernet Alliance President and Amphenol

Dave Stauffer, OIF

Nathan Tracy, Ethernet Alliance Board Member and TE Connectivity

Cathy Liu, Broadcom

Ramin Farjadrad, Marvell

Key Considerations Driving Electrical Interfaces

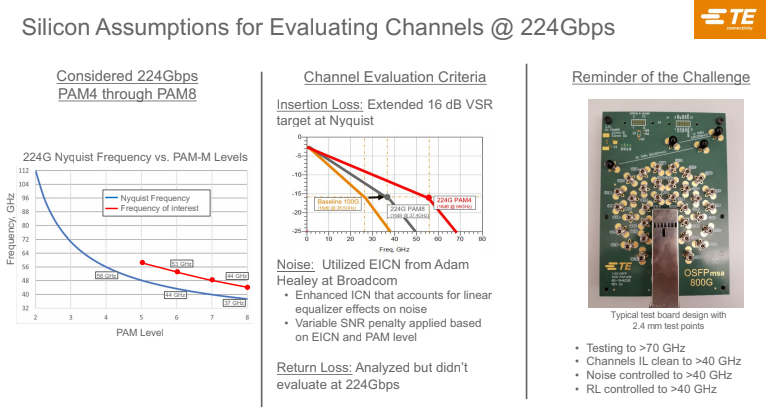

On day three of the Ethernet Alliance’s TEF21: The Road Ahead, panelists discussed the future of electrical interfaces. With faster speeds and next generation applications driving increased electrical data rates, the Next Generation Electrical Interfaces Beyond 100G moderator Chris Lyon, Ethernet Alliance Board President, along with panelists Dave Stauffer, OIF & Kandu Bus (OIF Common Electrical I/O 224G Project Overview); Nathan Tracy, Ethernet Alliance BoD and TE Connectivity (Electrical Future Work); Cathy Liu, Broadcom (Electrical Interfaces beyond 100G); and Ramin Farjadrad, Marvell (224G Dual Duplex Signaling over Single Lane Copper Links), addressed key issues and considerations surrounding the next industry rate and the interfaces needed to deliver it. Questions such as what reaches will be required, and which signaling modulation schemes will be necessary were discussed.

At the presentation’s conclusion, the audience engaged panelists with numerous questions about the technology developments needed to address escalating speed and bandwidth requirements impact on electrical interfaces. Their insightful responses are captured below in part one of a three-part series.

Investigating New Signaling Modulation Schemes

Investigating New Signaling Modulation Schemes

Chris Lyon: From an application and protocol perspective, is a FEC heavy PAM8 preferable to an analog heavy full duplex PAM4 implementation for 224 gigabits?

David Stauffer: I don’t know that we know the answer to which is better right now. That’s part of the trade-off being considered

Ramin Farjadrad: I guess it really depends on the channel and the quality of the channel and the complexity you are willing to pay on the fly.

Nathan Tracy: I agree. There’s always a certain set of trade-offs and we want to understand in the application space that we’re targeting, what’s the cost of those trade-offs and overall, what’s the right balance? And that’s really what the industry does in these early phases in organizations like the OIF and the IEEE. You know a challenge like that can be brought in and then you can have multiple people undertake the analysis and come back with multiple perspectives so that we, hopefully, vet out all these different possible derivative solutions to the one that will be optimal for the application that we’re intending. It’s very important that the industry provides that definition, and then, of course, the solid analysis to justify its solution.

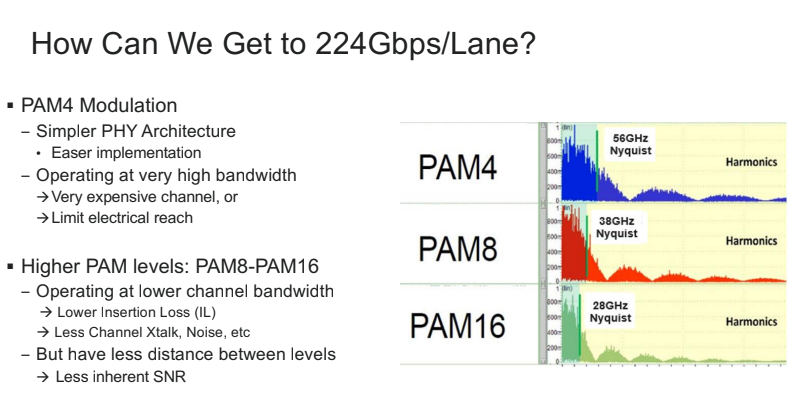

Cathy Liu: My point of view on what direction to go, with FEC, without FEC, or with heavy FEC with different modulations, with analog SerDes (Serializer/Deserializer) or DSP SerDes, or with Dual Duplex or traditional differential signal? These really cover different factors. If the latency is very critical, we cannot tolerate large latency, and cannot have stronger FEC to cover PAM8 SNR penalty. Also, power consumption is leading us to make the decision, for example, for very short reach or XSR, complicated equalizations or DSP vs. analog could give us the lower power solution. Many have come up with different architectural solutions, and also for the channel, what the channel can do versus what the SerDes can recover the signal, it’s really a chicken and egg dilemma. If the channel has bandwidth limitations, we may have to go with a higher modulation levels. If the channel can improve not only the bandwidth but cross talk at a certain level, we would like to go with the simpler, the better, right solution. So, it’s a chicken and egg problem, with quite a few things added as related and tangled. Then all parts of the industry from the chip vendors, component and system vendors can come together to analyze this next speed node so we can come up with the best solution.

Ramin Farjadrad: And of course, one thing to consider here as we go to a higher level of modulations from PAM4, if we try to use DFE in that link, we increase  the chances of error propagation and error burst. And that will impact the efficiency of FEC. So, of course, we need more complex FEC with higher gains, longer, better set of protections and so forth for higher level PAM, that degrades further from the link SNR. Those are the complexities that we have to have in mind as well.

the chances of error propagation and error burst. And that will impact the efficiency of FEC. So, of course, we need more complex FEC with higher gains, longer, better set of protections and so forth for higher level PAM, that degrades further from the link SNR. Those are the complexities that we have to have in mind as well.

Chris Lyon: How is the 224 gig PAM4 SNR with practical AFE only 4dB worse than the 112 gig PAM4 SNR? Will the echo canceller not cause much higher than 4dB noise increase due to uncancelled echo?

Ramin Farjadrad: It’s all about the question of how many echo taps, or how many– or how long your echo canceller filter is. You can create an echo canceller which is long enough with high enough resolution per tap that you completely cancel echo for any residual echo. So, in that scenario, for example in the slide that is on the screen right now, we have about 3dB delta between the two cases, and that’s at 128 taps. If we increase these taps to 1,000, that delta will be much less and comes down to maybe 1dB or less. So, it’s all about the tradeoff of the number of TAPS, the complexity that we want to spend there versus the SNR gain. But at the end of the day, if we spend enough complexity in design to cancel the residual echoes per tap, then the two will be very close in performance.

Chris Lyon: Is there any idea about using single-ended 112 gig PAM4 instead of differential 224 gig PAM4, 6 or 8?

Ramin Farjadrad: Single-ended always comes with concern of noise immunity, of course, depending on what the channel is, and if we can protect the channel from noise. So, in an XSR link, that if we can protect the channel from the noise, using differential over single-ended, the only advantage we get is doubling the signal amplitude, because you get plus/minus the subtraction of the two polarities. But if you go over external to or a cable over any other distance, then notice immunity crosstalk from other sources can be an issue. But that’s a good approach to do if we can protect the signal from external crosstalk.

David Stauffer: I would add to that, though, it’s not just protecting the signal from external crosstalk, it’s also not generating so much noise that the systems start failing EMI.

Nathan Tracy: Yes, for some of our simulation work, we have looked at single-ended channels where they’re very short, very simple media. You know, as soon as we get into any kind of a noisy environment, it doesn’t tend to pay off. So, one of the things that comes to mind for me is like the XSR channel where it’s very short channel, but yet, we have all the complexity or the impairments of the fan-out from the large ASIC, potentially. So, we have to do the analysis, but I don’t know that it would provide a net positive for the comparison.

Chris Lyon: Any additional thoughts you would like to share with everyone listening to this discussion?

Nathan Tracy: I can tell by all the questions that came in that you folks understand the challenges that we’re describing here to deal with 200 gigabits per second. I encourage everyone to stay closely engaged in each of the industry bodies and forums and bring your expertise and your contributions, whether it’s the end application or whether it’s the physics of a specific physical device, or even the coding trade-offs. It takes the whole industry to make sure we get this right. 200 gig is probably going to be the hardest thing that we’ve ever done. We really need the industry to be fully participative in OIF and the IEEE environments to help make that better, and to echo some of the other points, you know, 200 gig may be so hard that for the first time, this may be the case where, as Ramin suggested, we might not have a common solution across all the different reaches. It may not be all PAM4. And let’s keep an open mind to what are the ideas that are optimal. We’re always trying to look for the low-power, low-cost solution and that may be different for the first time in the industry across the different channels. Let’s keep an open mind and continue to contribute.

David Stauffer: I just wanted to thank Cathy and Nathan and Ramin for their presentations. As you can see there’s no clear consensus yet on where 224 gigs should go, or how we’re going to solve it. I’m sure we’ll get to a solution, and as Nathan said, it may very well be tailored for each reach at this point, but these are the conversations that have to happen. They have to happen over the next few months this year in order to make progress and get the standards in place in time. I again invite people to OAF to help see the research and participate in the discussion.

To access TEF21: Next Generation Electrical Interfaces on demand, and all of the TEF21 on-demand content, visit the Ethernet Alliance website.